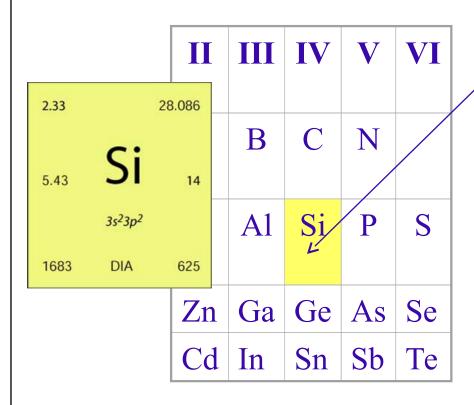

Silicon (Si) – the dominating material in IC manufacturing

#### Compound semiconductors\_

#### III - V group:

- ♦ GaAs

- ♦ GaN

- ♦ GaSb

- ♦ GaP

- ♦ InAs

- ♦ InP

- ♦ InSb

......

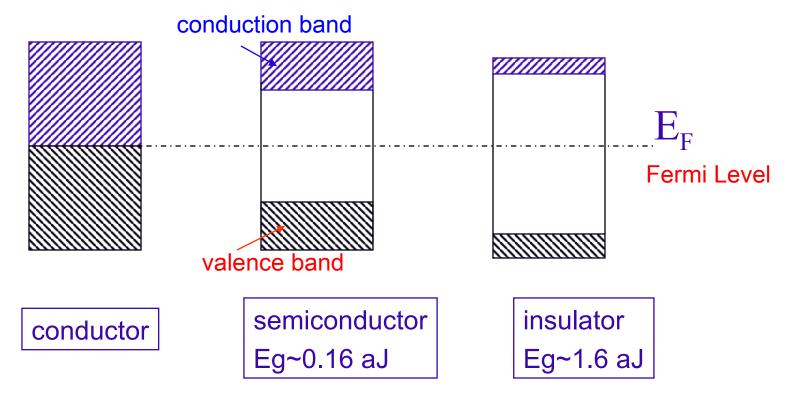

#### The Energy Band Structure

| Material      | Electrical conductivity σ                                                         |

|---------------|-----------------------------------------------------------------------------------|

| Metal         | $\sigma > 10^5 \Omega^{-1} \text{m}^{-1}$                                         |

| Semiconductor | $10^5 \ \Omega^{-1} \text{m}^{-1} > \sigma > 10^{-8} \ \Omega^{-1} \text{m}^{-1}$ |

| Insulator     | $\sigma < 10^{-8} \ \Omega^{-1} \text{m}^{-1}$                                    |

#### **Controlling Conductivity**

$$\sigma = qn\mu$$

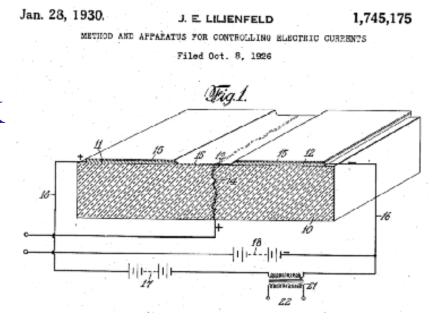

## MOS Transistor transfer resistor

1930 J. Lilienfend applied for a patent regarding a field-effect device in USA

1935 O. Heil - similar patent in UK

1960 Practical manufacturing of a field-effect transistor

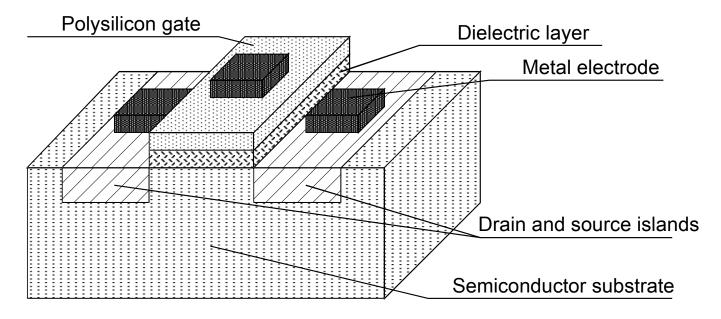

#### **MOS Transistor**

Metal Oxide Semiconductor

Various names: MOSFET, MIS, IGFET

$\rho$  of the substrate: 0.01 - 0.1  $\Omega$ m

n+ concentration: 10<sup>24</sup> - 10<sup>26</sup> m<sup>-3</sup>

$t_{ox}$ : 1-100 nm

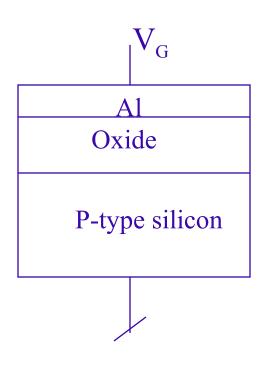

#### The MOS Capacitor

- ♦ Accumulation V<sub>G</sub><0

- ◆ Depletion V<sub>G</sub>>0

- ♦ Inversion V<sub>G</sub>>>0

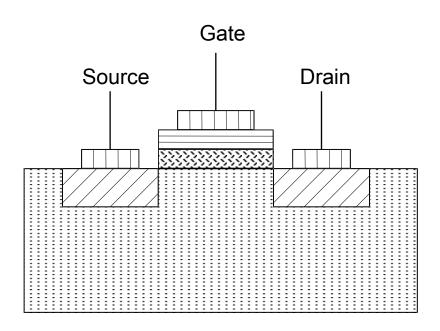

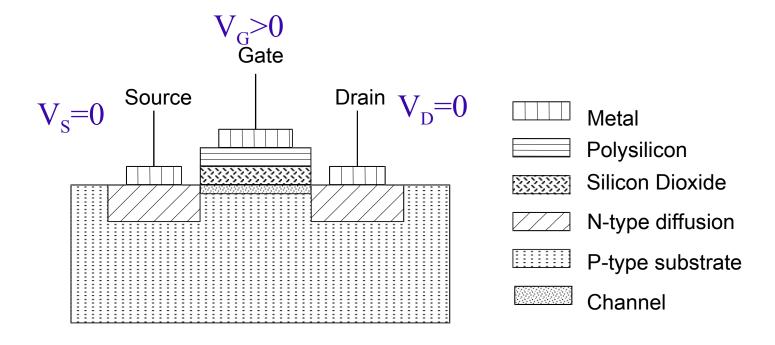

#### nMOS Cross-section

Metal

Polysilicon

Silicon dioxide

N-type diffusion

P-type substrate

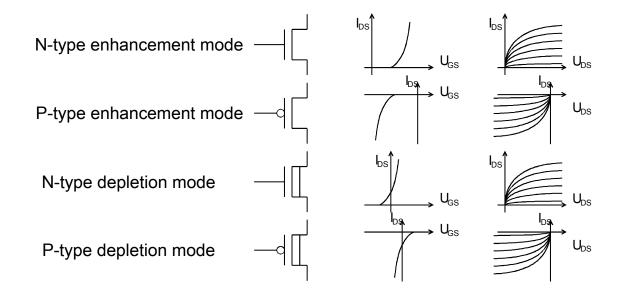

#### Classification of MOS Transistors

N-channel P-channel

Depletion mode Enhancement mode

## nMOS Transistor with Biased Gate

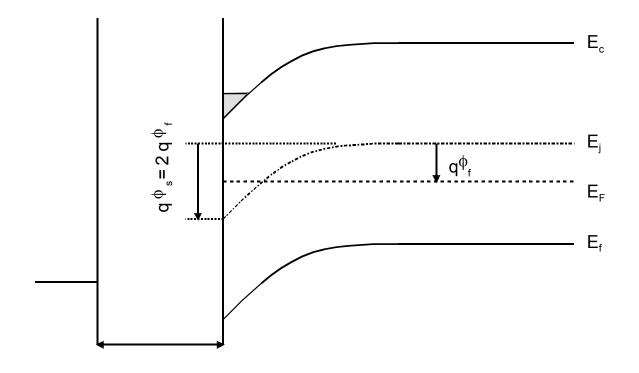

# Beginning of The Strong Inversion $V_G = V_T$

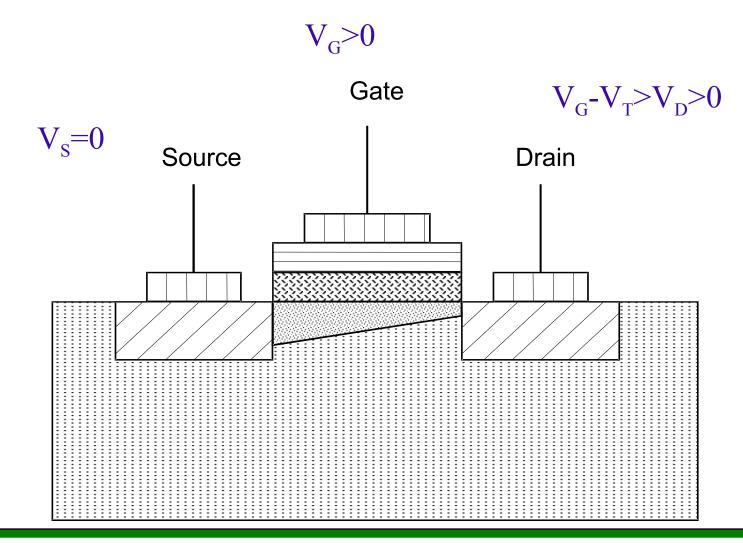

### Conducting nMOS Transistor

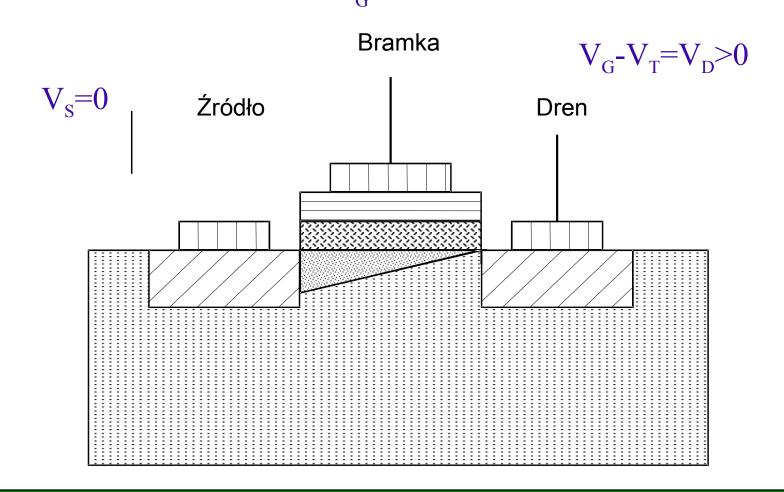

# Conducting nMOS at The Beginning of Saturation

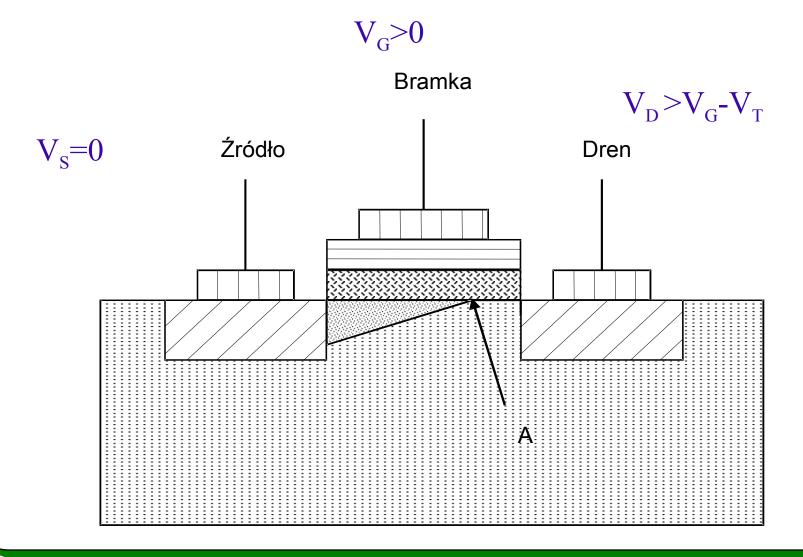

#### Saturated nMOS Transistor

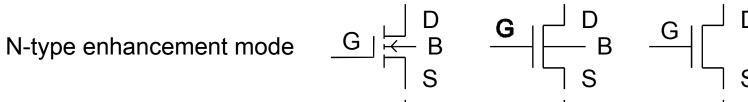

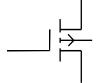

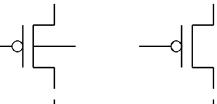

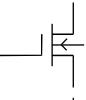

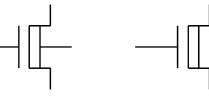

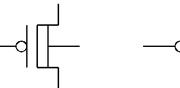

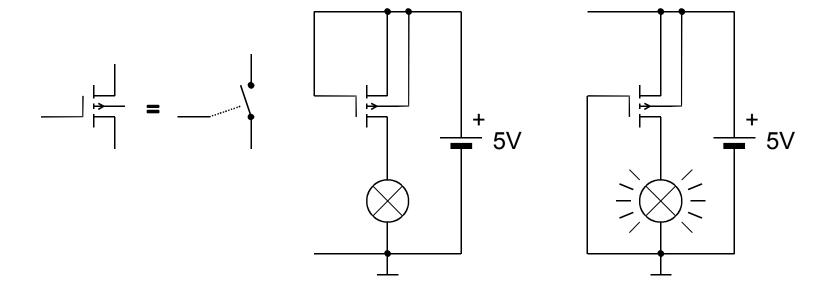

#### MOS Symbols

P-type enhancement mode

N-type depletion mode

P-type depletion mode

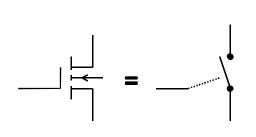

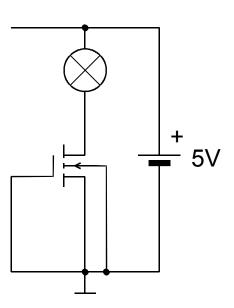

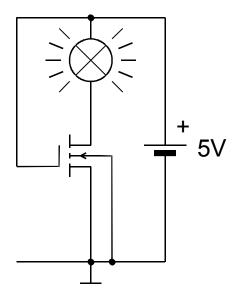

#### nMOS as A Switch

#### pMOS as A Switch

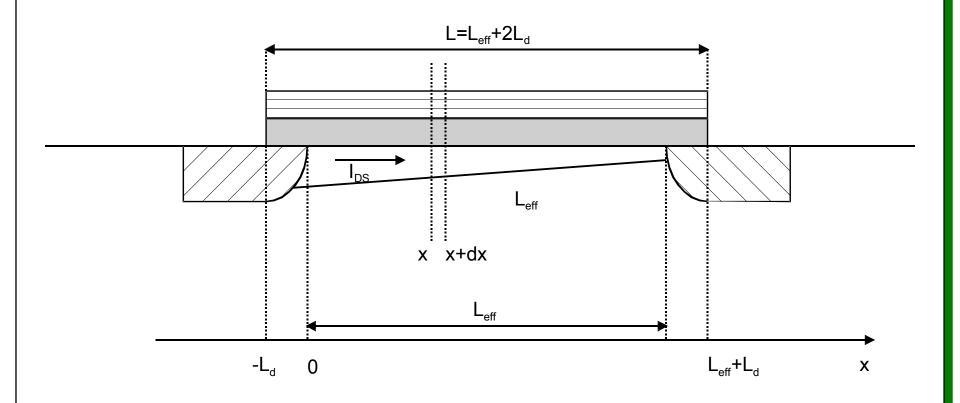

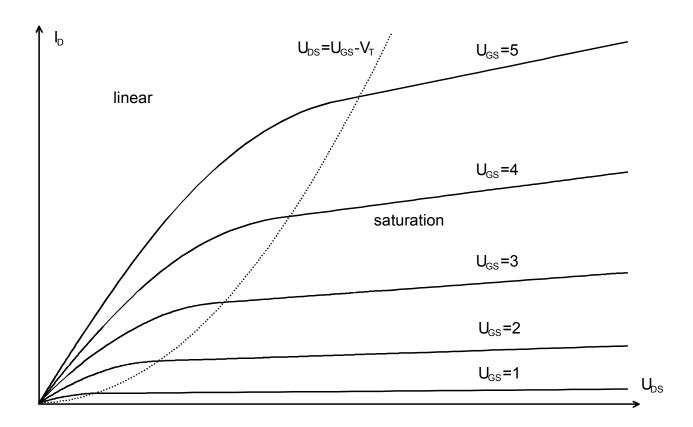

#### MOS in Linear Range

$$I_{DS} = \mu \frac{W_{eff}}{L_{eff}} C_{ox} \int_{0}^{U_{DS}} (U_{GS} - V_{T0} - V(x)) dV$$

$$I_{DS} = \mu \frac{W_{eff}}{L_{eff}} C_{ox} ((U_{GS} - V_{T0})U_{DS} - \frac{1}{2}U_{DS}^{2})$$

$$I_{DS} = k_p \frac{W_{eff}}{L_{eff}} ((U_{GS} - V_{T0})U_{DS} - \frac{1}{2}U_{DS}^2)$$

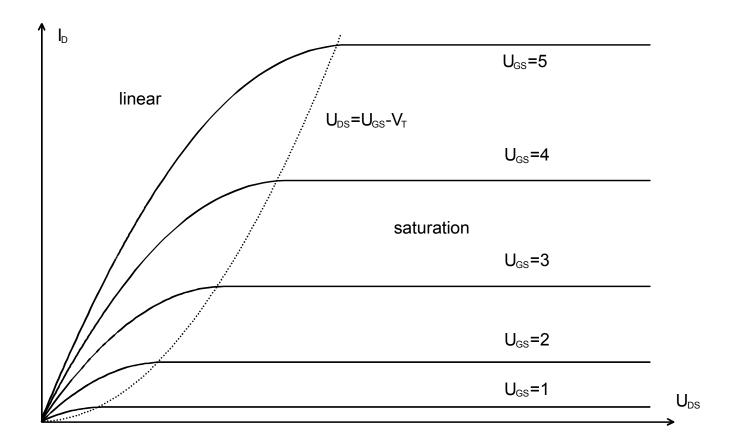

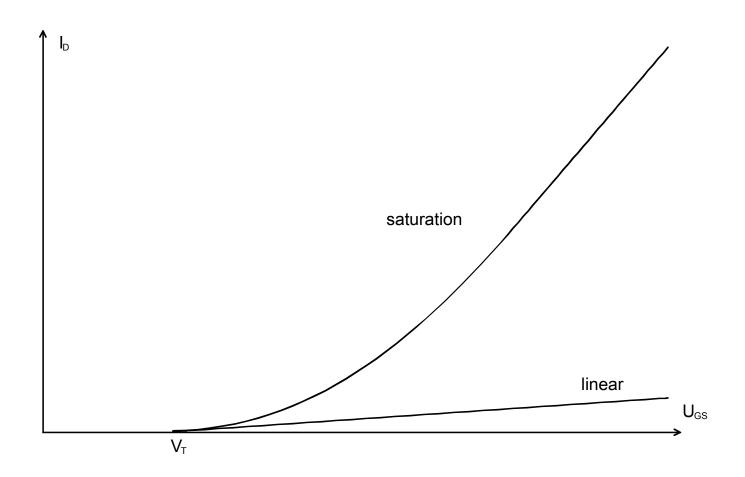

Linear

$$I_{DS} = \frac{k_p}{2} \frac{W_{eff}}{L_{eff}} (U_{GS} - V_{T0})^2$$

Saturation

$\beta = \mu \epsilon / t_{ox}(W/L)$  Transistor gain factor

$V_{T0} = U_{FB} + 2|\phi_f| + \frac{\sqrt{2q\varepsilon_{si}N_a(2|\phi_f|)}}{C_{ox}}$

R

$$V_T = V_{T0} + \gamma \left( \sqrt{|U_{BS}| + 2|\phi_f|} - \sqrt{2|\phi_f|} \right)$$

$$\gamma = \frac{\sqrt{2q\varepsilon_{si}N_a}}{C_{ox}}$$

#### MOS Output Characteristics

#### **MOS Transfer Characteristics**

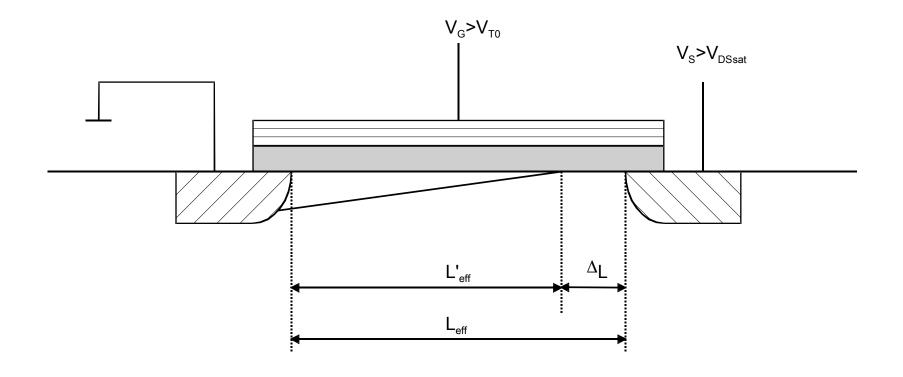

### **Channel Length Modulation**

#### Model LEVEL1

# SPICE DC Parameters for 1µm MOS

| Parameter | nMOS                 | pMOS               | Units                   | Description                           |

|-----------|----------------------|--------------------|-------------------------|---------------------------------------|

| VTO       | 0.7                  | 0.7                | volt                    | Threshold voltage                     |

| KP        | 8*10 <sup>-5</sup>   | 2.5*10⁻⁵           | A/V <sup>2</sup>        | Transconductance coefficient          |

| GAMMA     | 0.4                  | 0.5                | <b>V</b> <sup>0.5</sup> | Bulk threshold parameter              |

| PHI       | 0.37                 | 0.36               | volt                    | Surface potential at strong inversion |

| LAMBDA    | 0.01                 | 0.01               | volt <sup>-1</sup>      | Channel length modulation parameter   |

| LD        | 0.1*10 <sup>-6</sup> | 0.1*10-6           | meter                   | Lateral diffusion                     |

| тох       | 2*10-8               | 2*10-8             | meter                   | Oxide thickness                       |

| NSUB      | 2*10 <sup>16</sup>   | 4*10 <sup>16</sup> | 1/cm³                   | Substrate doping density              |

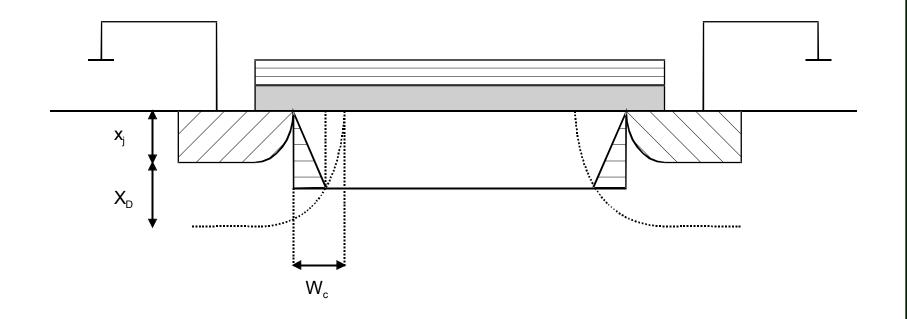

#### What's new in LEVEL3

- Modified threshold voltage model, taking into account the drain induced barrier lowering (DIBL)

- Longitudinal and transversal electric field dependent mobility model

- Improved channel length modulation and saturation voltage model

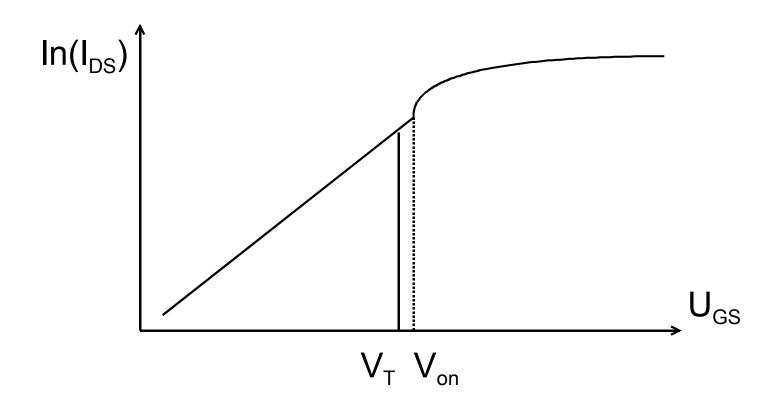

- Weak inversion (subthreshold) range

# Trapezoidal Charge Approximation

#### Subthreshold Range

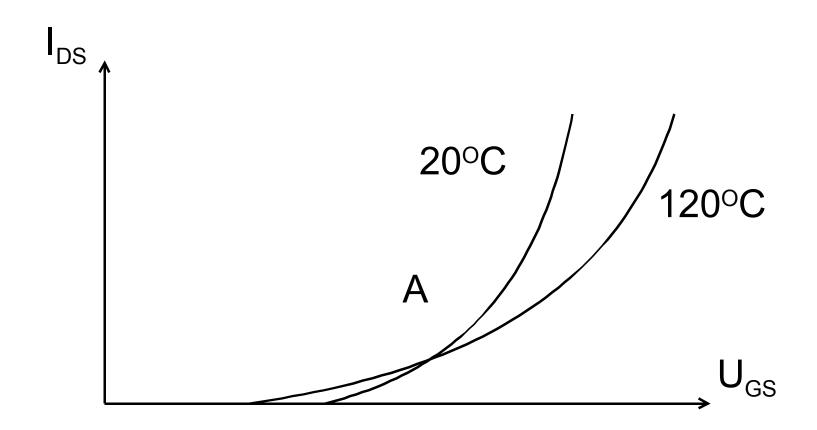

## Temperature Influence on MOS Characteristics

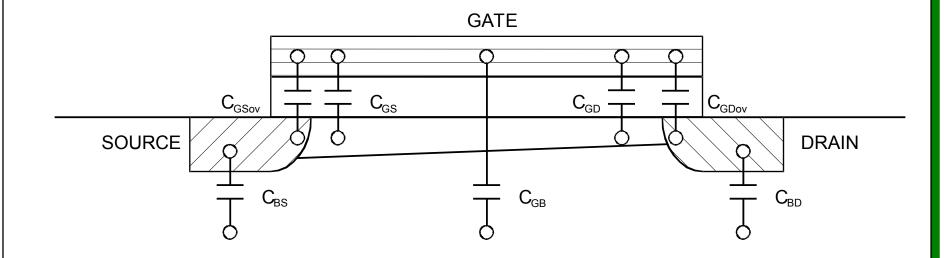

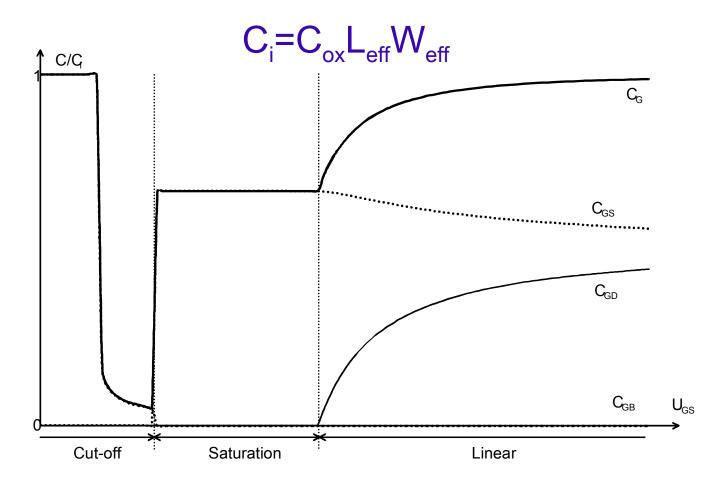

### **MOS Capacitances**

#### MOS Capacitancies

#### **MOS Capacitances**

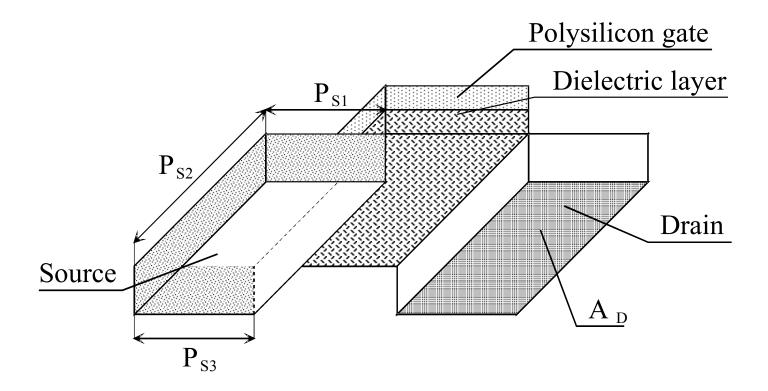

$$C_{BD} = \frac{C_{j}A_{D}}{\left(1 - \frac{U_{BD}}{\phi_{j}}\right)^{M_{j}}} + \frac{C_{jsw}P_{D}}{\left(1 - \frac{U_{BD}}{\phi_{j}}\right)^{M_{jsw}}} \qquad C_{BS} = \frac{C_{j}A_{S}}{\left(1 - \frac{U_{BS}}{\phi_{j}}\right)^{M_{j}}} + \frac{C_{jsw}P_{S}}{\left(1 - \frac{U_{BS}}{\phi_{j}}\right)^{M_{jsw}}}$$

$$C_{BS} = \frac{C_j A_S}{\left(1 - \frac{U_{BS}}{\phi_j}\right)^{M_j}} + \frac{C_{jsw} P_S}{\left(1 - \frac{U_{BS}}{\phi_j}\right)^{M_{jsw}}}$$

$$C_{GDov} = C_{GDO} W_{eff}$$

$$C_{GSov} = C_{GSO}W_{eff}$$

$$C_{GSO} = C_{GDO} = C_{ox}L_d$$

Accumulation

$$C_{GB} = C_{ox} W_{eff} L_{eff}$$

Depletion

$$C_{GB} = \frac{C_{ox}W_{eff}L_{eff}}{\sqrt{1 + 4\left(\frac{U_{GB} - U_{FB}}{\gamma^2}\right)}}$$

#### **MOS Capacitances**

Linear range  $(C_{GB} = 0)$

$$C_{GS} = \frac{2}{3} C_{ox} W_{eff} L_{eff} \left( 1 - \frac{(U_{GS} - U_T)^2}{(U_{GS} - U_T + U_{GD} - U_T)^2} \right)$$

$$C_{GD} = \frac{2}{3} C_{ox} W_{eff} L_{eff} \left( 1 - \frac{(U_{GD} - U_T)^2}{(U_{GS} - U_T + U_{GD} - U_T)^2} \right)$$

for

$$U_{GS} \approx U_{GD}$$

$C_{GS} \approx C_{GD} \approx \frac{1}{2} C_{ox} W_{eff} L_{eff}$

Saturation range  $(C_{GD} = 0)$

$$C_{GS} = \frac{2}{3} C_{ox} W_{eff} L_{eff}$$

## Capacitance-Voltage Characteristics

#### What's Missing in LEVEL3

- Hot carrier effect

- Punch-through

- Non-uniform substrate doping

### MOS - Summary

| Operation range                | Pin voltages                           |

|--------------------------------|----------------------------------------|

| Cut-off                        | $U_{GS} < U_{FB}$                      |

| Linear, non-saturation, triode | $U_{GS} \ge V_T i U_{DS} < U_{Dsat}$   |

| Saturation, pentode            | $U_{GS} \ge V_T i U_{DS} \ge U_{Dsat}$ |

| Sub-threshold, weak inversion  | $U_{FB} \leq U_{GS} < V_T$             |