Microelectronics

## MICROELECTRONICS

Grzegorz Jabłoński Department of Microelectronics and Computer Science Building B-18, room 33 gwj@dmcs.p.lodz.pl

- A.S. Sedra, K.C. Smith, "Microelectronic Circuits", 7th Ed., Oxford University Press, 2014

- Michael John Sebastian Smith, "Application-Specific Integrated Circuits", Addison-Wesley 1997

- I. Sutherland, B. Sproull, D. Harris, "Logical Effort -Designing Fast CMOS Circuits", Morgan Kaufmann Publishers 1999; http://www.mkp.com/Logical\_Effort

- M. Napieralska, G. Jabłoński "Podstawy mikroelektroniki" Łódź 2002, ISBN 83-89003-01-5

- http://fiona.dmcs.p.lodz.pl/micro

- Introduction

- The MOS Transistor

- Integrated Circuits (IC) Manufacturing Technologies

- MOS Digital Circuit Families

- Delay Calculation in CMOS Circuits Logical Effort

- IC Design Methodologies

- MICROELECTRONICS [gr.], branch of electronics dealing with operation, construction and technology of → integrated circuits.

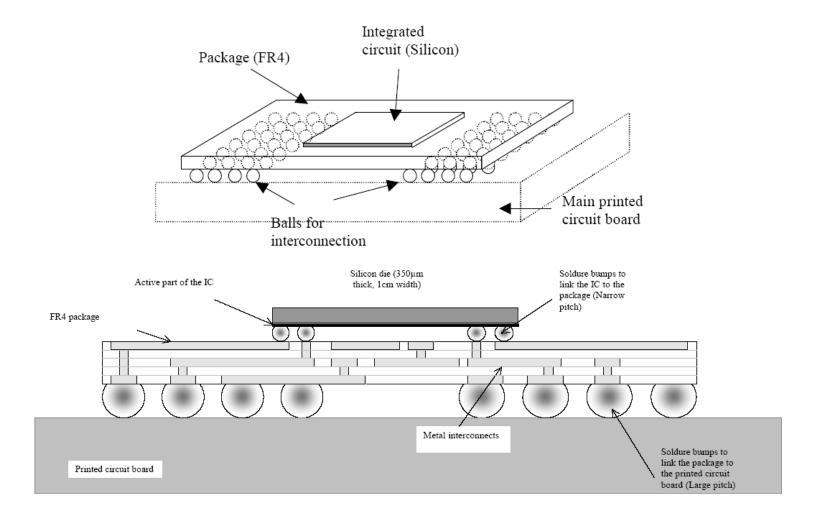

- **INTEGRATED CIRCUIT**, miniature electronic circuit, which part or all components are manufactured together with the interconnections in one technological cycle in or on the surface of a common substrate.

# The History of Computing

### Mechanical

- Abacus 3000 BC

- Adding machine: B. Pascal 1642

- Multiplying machine: G. Leibniz 1694

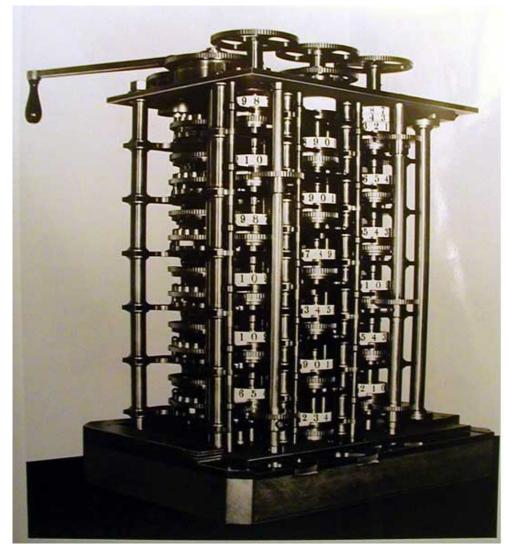

- Difference engine: Charles Babbage 1823

- Analytical machine: Charles Babbage 1833

- The mill (CPU), the store (memory), control, punched card reader, card puncher

- Control from the external source (punched cards)

- Ada (Byron) Lovelace considered a world's first programmer

#### Microelectronics

- Electromechanical calculator with punched cards H. Hollerith 1890.

- Electromechanical calculator Mark I 1944

- H. Aiken: 1937-1944, USA, Harvard University + IBM

- 750 000 components, 900 km of wires, weight 5 T

- addition 0.3 s, multiplication 6 s

#### Mark II - "Computer Bug" (Grace Hopper)

Photo # NH 96566-KN First Computer "Bug", 1945 92 9/9 andon started 0800 1.2700 9.037 847 025 1000 stopped - andam 9.037 846 95 const 16415 (-2) 4.615925059(-2) 13" UC (032) MP - MC (033) PRO 2 2.130476415 const 2.13067641 Relans 6-2 m 033 failed special special test In tel Relays cho 1100 Started Losine Tape (Sine check) 1525 forted Multy Adder Test Relay #70 Panel F (moth) in relay. 1545 1700 cloud dom.

9

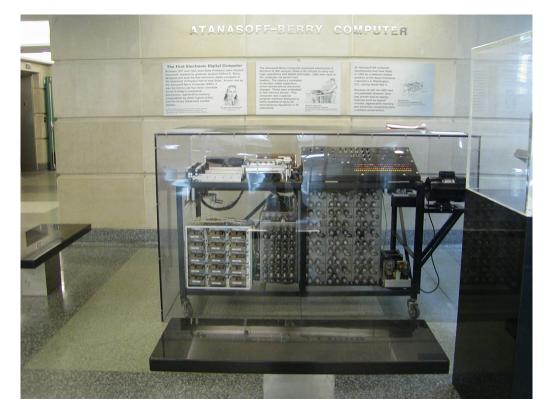

1941 – John Atanasoff and Clifford Berry -ABC (calculator) – vacuum tubes

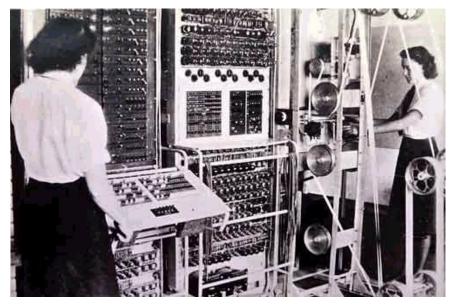

- 1943 Colossus code cracking calculator (1500 vacuum tubes)

- data on perforated paper tape

- 1944 Colossus 2 (2500 tubes)

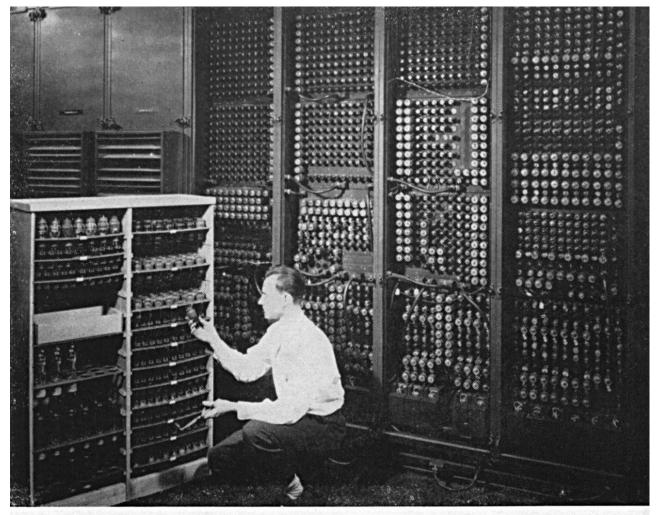

- 1943-1946 ENIAC the first electronic computer

- Electronic Numerical Integrator And Computer

- John Eckert, John Mauchly

- 18 000 vacuum tubes, 70 000 resistors, 1500 relais, weight 30 T,

- Power consumption 174 kW, cost 750 000 \$

- Addition: 0.2 ms

- Numbers encoded in decimal, every digit stored in 10position counter (36 tubes), 10 digits stored in an accumulator.

- The whole machine: 20 accumulators.

- The control of the machine operation: setting 10-position electric switches

Replacing a bad tube meant checking among ENIAC's 19,000 possibilities.

- 1944 1949 EDVAC John von Neumann et al

- Electronic Discrete Variable Automatic Computer

- stored program machine;

- basic components:

- arithmetical and logical unit, memory, input, output, control

- binary system

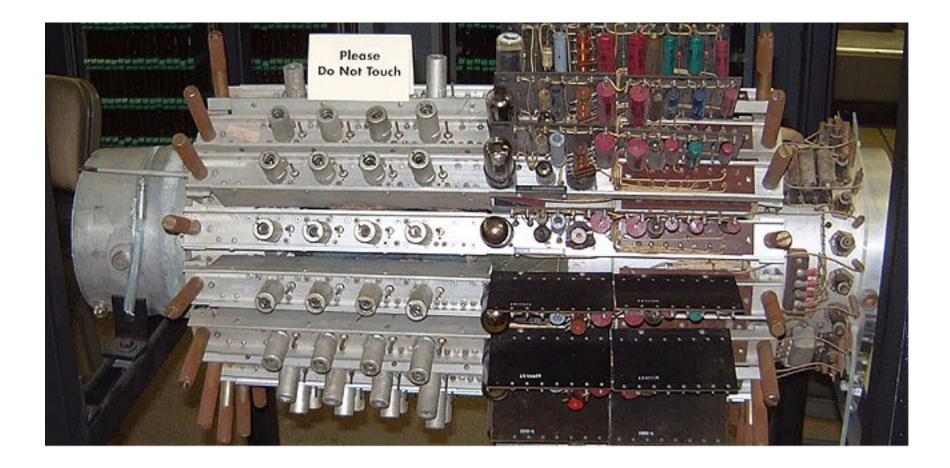

- memory mercury delay line

- 1951 UNIVAC I first successfull commercial computer

### Mercury Memory

15

- Technology:

- digital circuits: transistors

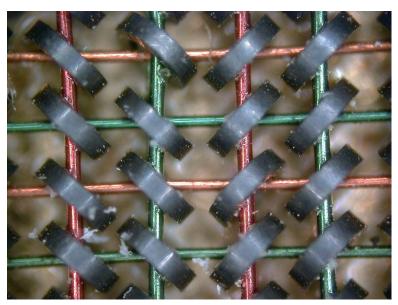

- memories: drum memory (initially), ferrite memory

- Technology:

- Digital circuits: low and medium scale of integration integrated circuits

- Memories: ferrite memory (initially), integrated circuits

- Interesting dates:

- 1965 IBM 360

- 1971 IBM 370 70 % of computer market

- 1968 PDP-8 12-bit minicomputer with a bus architecture

- 1970 PDP 11 16-bit minicomputer with a bus architecture

- 1972 Illiac IV matrix computer with 64 processing units

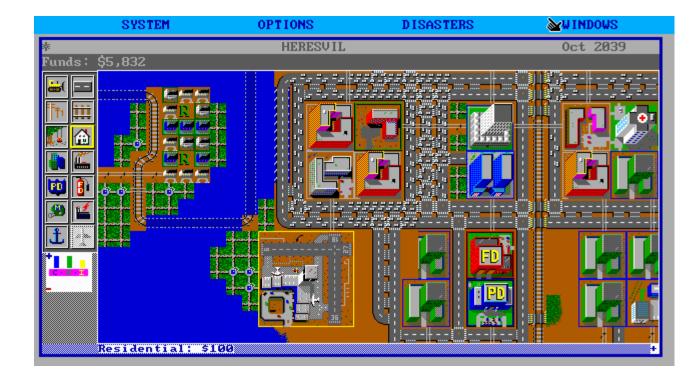

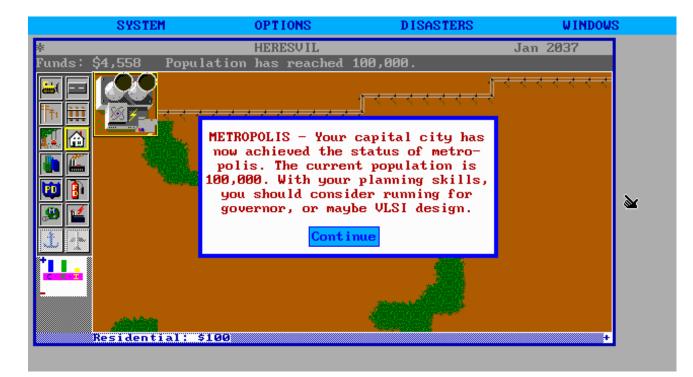

- Technology:

- Digital circuits: very-large scale of integration digital circuits

- Memories: VLSI circuits

### **History of Electronics**

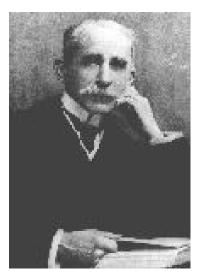

Ambrose Fleming at Marconi Company patents the two-electrode radio rectifier, which he called the thermionic valve; it is also known as the vacuum diode, kenotron, thermionic tube, and Fleming valve.

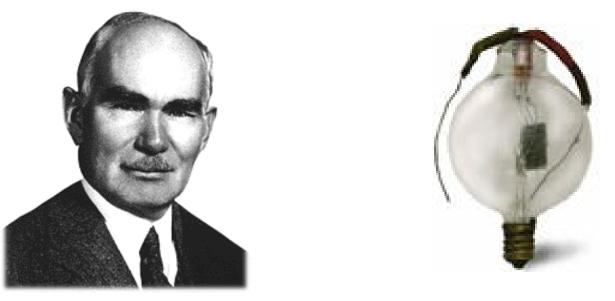

Lee De Forest devises a three-electrode tube, or triode; the device is capable of detecting and amplifying radio signals. It was also known as an 'Audion valve'.

On December 23, 1947 William Shockley, Walter Brattain and John Bardeen at Bell Labs demonstrate their new invention of the pointcontact transistor amplifier. The name transistor is short for "transfer resistance".

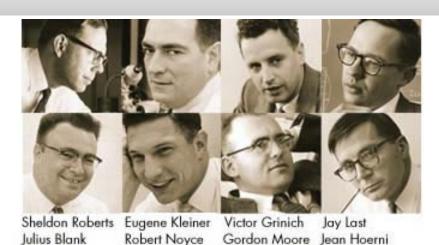

William Shockley, co-inventor of the transistor seven years earlier, founds Shockley Semiconductor Laboratories in Santa Clara Valley. He recruits 12 young scientists dedicated to the use of germanium and silicon for transistors -- his "Ph.D. production line." Shockley wins the Nobel Prize for Physics in 1956, but his management style and disenchantment with pure research causes the eight young scientists to leave company.

Gordon E. Moore, C. Sheldon Roberts, Eugene Kleiner, Robert N. Noyce, Victor H. Grinich, Julius Blank, Jean A. Hoerni and Jay T. Last - the "Traitorous Eight" from Shockley Semiconductor - use \$3500 of their own money to develop a method of mass-producing silicon transistors using a double diffusion technique and a chemical-etching system.

The silicon and germanium mesa allows manufacturers to produce multiple transistors on a single wafer.

Fairchild Camera and Instrument Corporation invests \$1.5 million in return for an option to buy the company within eight years. On October 1, 1957, Fairchild Semiconductor is born. The new company is profitable in six months with the help of its first sale: an order from IBM<sup>™</sup> for 100 transistors at \$150 a piece.

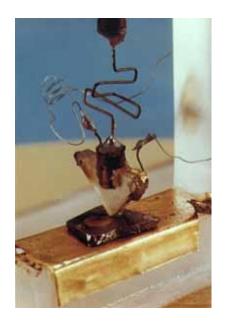

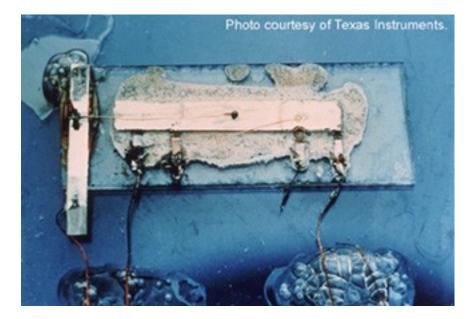

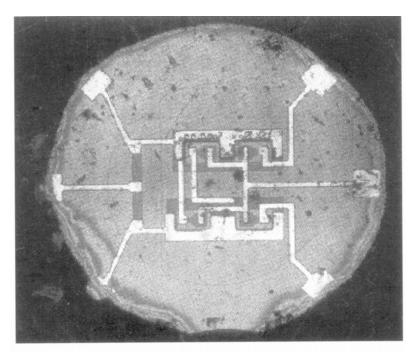

At Texas Instruments, Jack Kilby builds the first integrated circuit – an oscillator consisting of one transistor, two resistors and one capacitor – all of them made of germanium.

On September 12, 1958, Texas Instruments executives gathered around Kilby's oscillator, a complete circuit on a chip less than half an inch long. Kilby pushed the switch, and a bright green thread of light snaked across the screen. The integrated circuit worked, and a new era in microelectronics was born.

Jean Hoerni at Fairchild Semiconductors invents a planar transistor, where a collector, base and emitter are all on one plane. Using this device, Robert Noyce develops the monolithic integrated circuit -- a flip-flop consisting of six devices on a fingernail-size wafer of silicon. Today, nearly fifty years later, the planar process is the primary method for producing transistors.

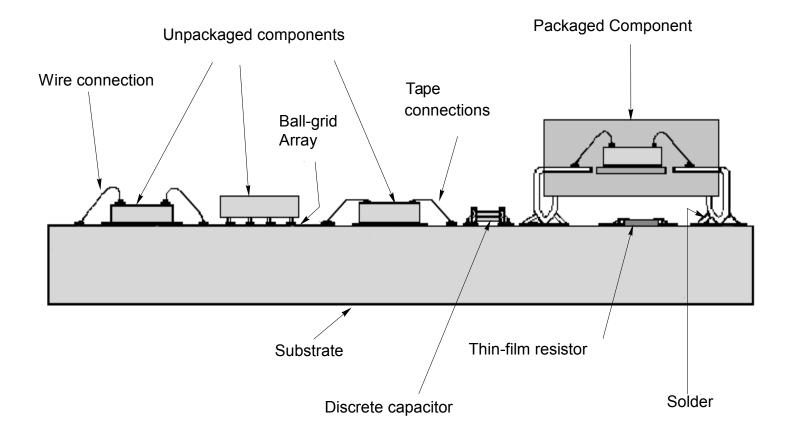

- Hybrid

Thick-film

Thin-film

- Monolithic

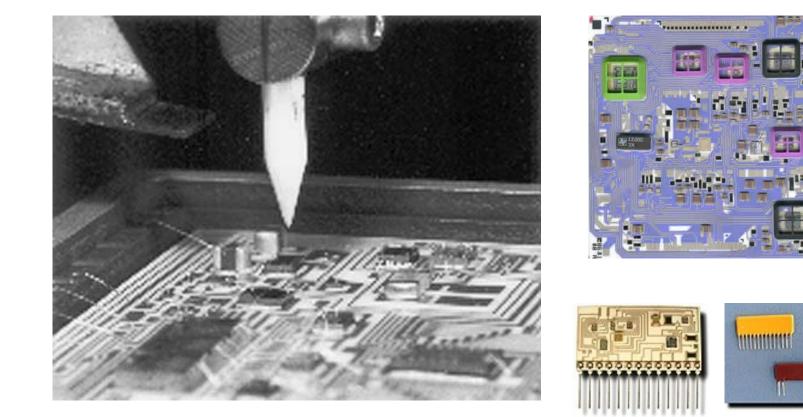

### Thick-Film Circuits

₽⊬

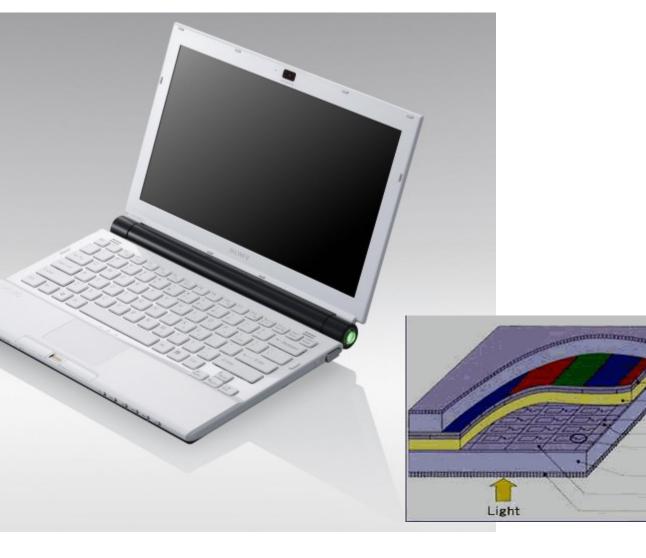

Polaizer film Upper glass substrate Color filter Transparent electrodes Liquid crystal display Signal electrodes Scanning electrodes Thin Film Transistor(TFT) Lower glass substrate Transparent electrodes Polaizer film

### **Monolithic Circuits**

### **Monolithic Circuits**

### Advantages of Integrated Circuits

- Low cost

- Low size

- High quality and reliability

- Same temperature characteristics of all the components

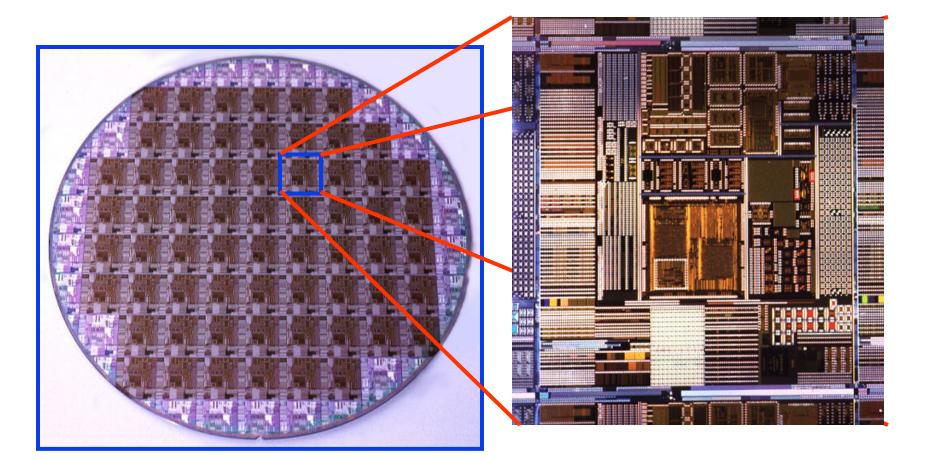

- The 60's: First ICs

- The 70's: Microprocessors

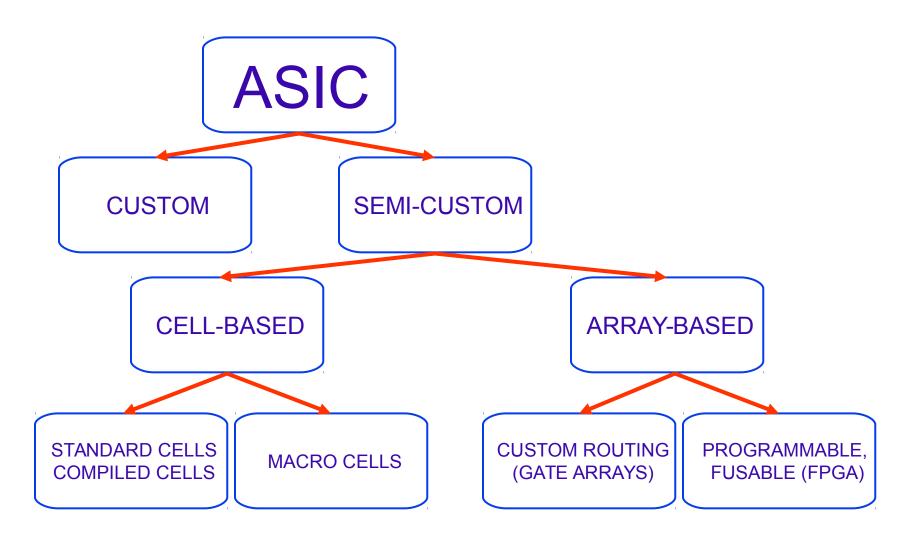

- The 80's: ASICs (Application Specific Integrated Circuits)

- The 90's: Micro Electro-Mechanical Systems (MEMS)

- The 2000's: System on Chip

- 1958 First IC (J. Kilby T.I.)

- 1960 First comercial IC logic RTL circuits MICROLOGIC - (Fairchild)

- 1964 TTL circuits (series 54 i 74 Texas Instruments)

- 1965 First Operational Amplifier µA 702 (Fairchild)

- 1967 OPAMP with high input impedance  $\mu$ A 709, first comparator  $\mu$ A 710

- 1967 First ROM memory 64 bits (MOS technology, Fairchild)

1968 µA 741

1968 OPAMP with input JFET transistors

1968 CMOS technology (RCA), calculators, watches, ...

1968 ROM memory 1024 bits (PHILCO)

37

#### The 70's - Microprocessor Development

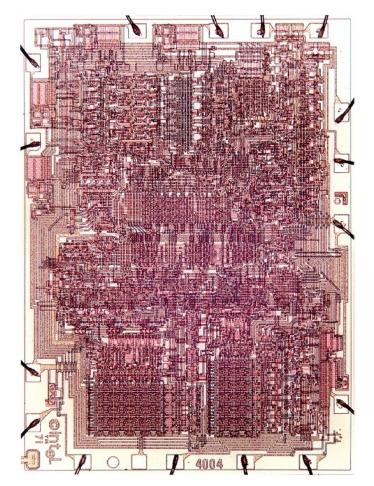

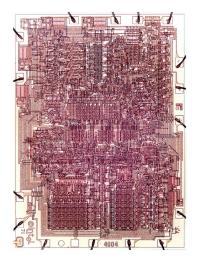

- 1971 INTEL first commercial 4 bit microprocessor 4004, with 45 instructions. PMOS Technology, 2300 transistors

- 1972 First 8 bit microprocessor 8008 (INTEL).

- 1973 INTEL 8080, NMOS technology, improved by Zilog - Z80

- 1974 First CMOS microprocessor-1802 (RCA).

- 1974 MOTOROLA 6800 single 5V supply voltage.

- 1976 First microcontroller 8048 (INTEL).

#### Intel 4004

#### 2,300 transistors

- 10-micron technology

- 46 instructions

- 40,000 instructions per second

- 4-bit data/address bus.

- 4-bit accumulator with separate carry and test bits,

- Sixteen 4-bit 'scratch-pad' registers (which can be used as eight 8-bit registers),

- A 12-bit PC (program counter), and three more 12-bit registers comprising an address stack

In 1972 on board of Pioneer 10, until 1998 the most distant human-made object (currently Voyager 1)

- 1978 INTEL 8086

- 1982 INTEL 80286

- 1989 INTEL 80486

- 1993 INTEL Pentium

- 1999 INTEL Pentium III

- 2000 INTEL Pentium 4

- 2004 INTEL Itanium 2

- 2006 INTEL Core Duo Processor

- 2007 INTEL Core 2 Quad Processor

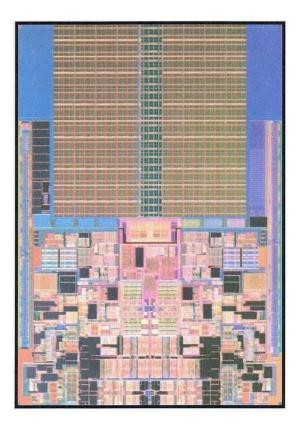

Photo of a die of dual-core Intel Penryn processor (45 nm) introduced in second half of 2007

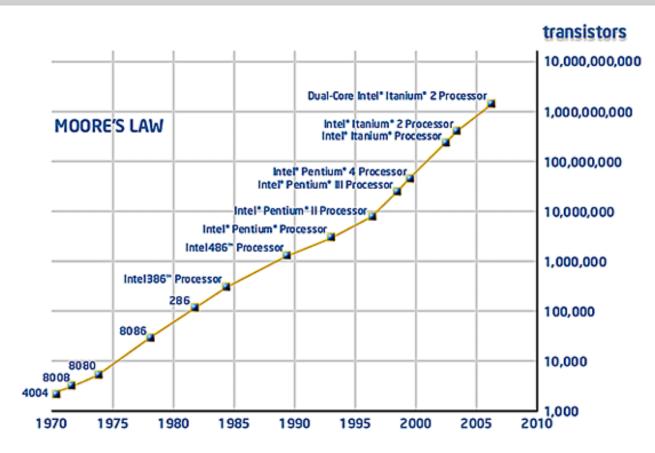

#### Number of Transistors in Different Processors

| Year of introduction | Processor                               | Number of transistors |

|----------------------|-----------------------------------------|-----------------------|

| 1971                 | 4004                                    | 2,300                 |

| 1972                 | 8008                                    | 2,500                 |

| 1974                 | 8080                                    | 4,500                 |

| 1978                 | 8086                                    | 29,000                |

| 1982                 | Intel286                                | 134,000               |

| 1985                 | Intel386™ processor                     | 275,000               |

| 1989                 | Intel486™ processor                     | 1,200,000             |

| 1993                 | Intel® Pentium® processor               | 3,100,000             |

| 1997                 | Intel® Pentium® II processor            | 7,500,000             |

| 1999                 | Intel® Pentium® III processor           | 9,500,000             |

| 2000                 | Intel® Pentium® 4 processor             | 42,000,000            |

| 2001                 | Intel® Itanium® processor               | 25,000,000            |

| 2002                 | Intel® Itanium® 2 processor             | 220,000,000           |

| 2004                 | Intel® Itanium® 2 processor (9MB cache) | 592,000,000           |

| 2006                 | Dual-Core Intel Itanium 2               | 1,720,000,000         |

| 2010                 | Quad-Core Intel Itanium                 | 2,046,000,000         |

#### Moore's Law

Moore's Law (1965) – number of transistors in an integrated circuit doubles every 18 months

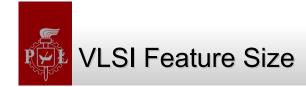

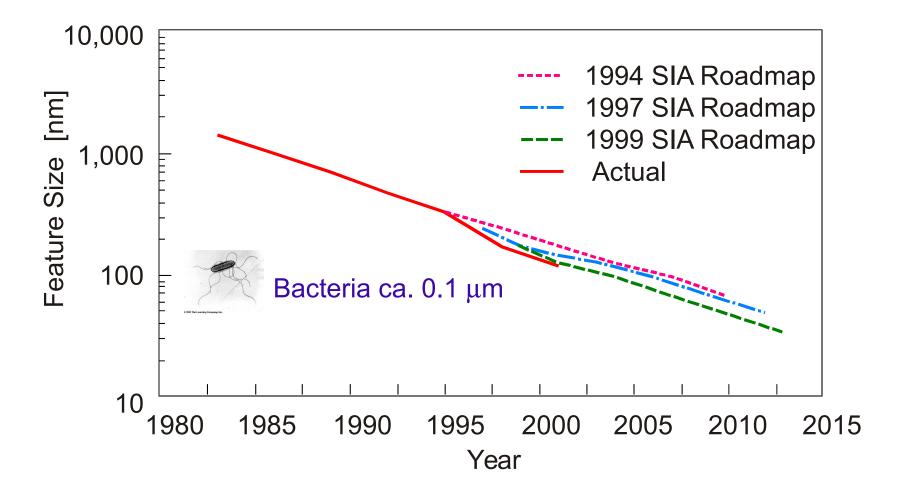

# **Rising Fab Costs**

Source: Dataquest, UMC

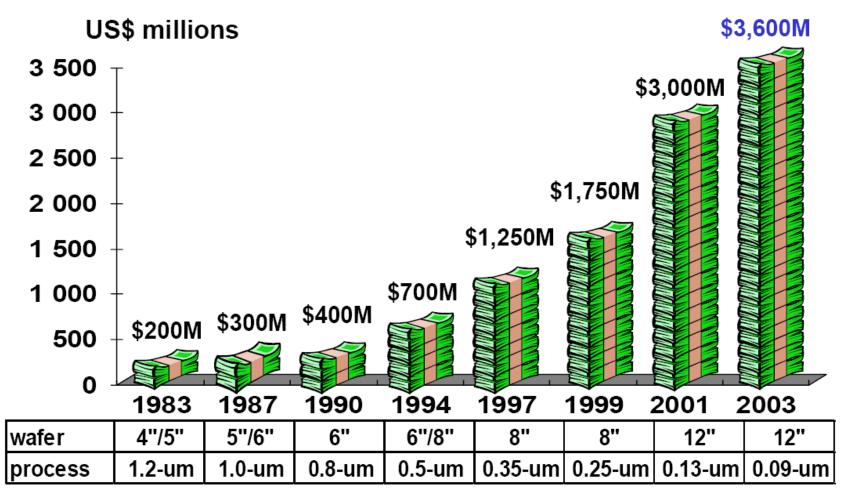

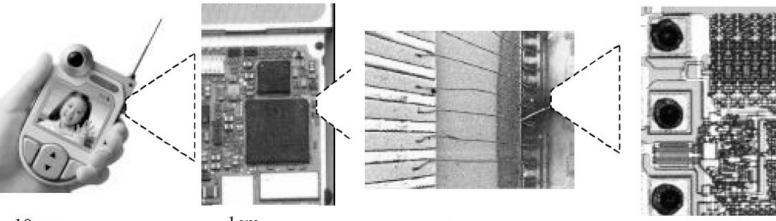

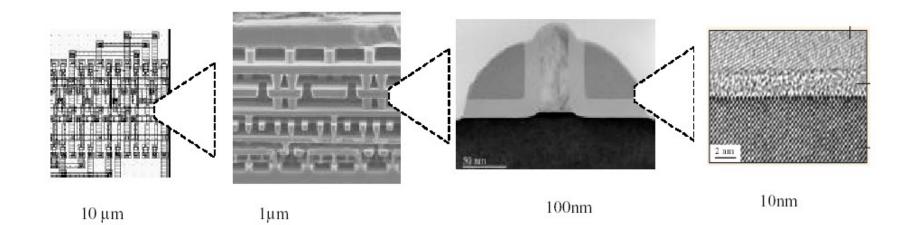

#### Miniaturization

10cm

$1 \mathrm{cm}$

$1 \mathrm{mm}$

- Basic parameters

- Logic gate delay

- Power dissipation

- Synthetic parameter – Power-delay product

- Standard

- Application Specific Integrated Circuits (ASIC)

- Application Specific Standard Product (ASSP)

- Advantages of Standard ICs

- Low cost

- "Off-the-shelf" availability

- Known reliability

- Many suppliers (usually)

- Disadvantages of Standard ICs

- Not optimized for a specific system

- Hard to create a unique product

- High area consumption

- Semicustom

- Interconnection masks customized

- Custom

- All masks customized

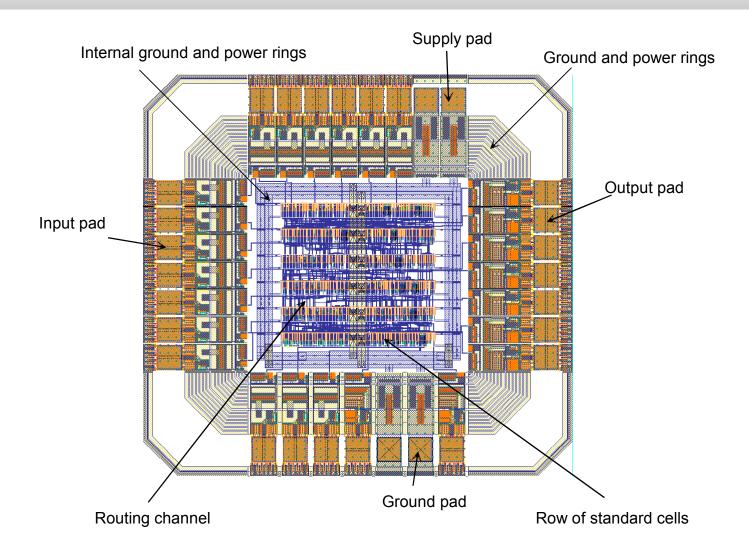

- Standard Cell

- Full Custom

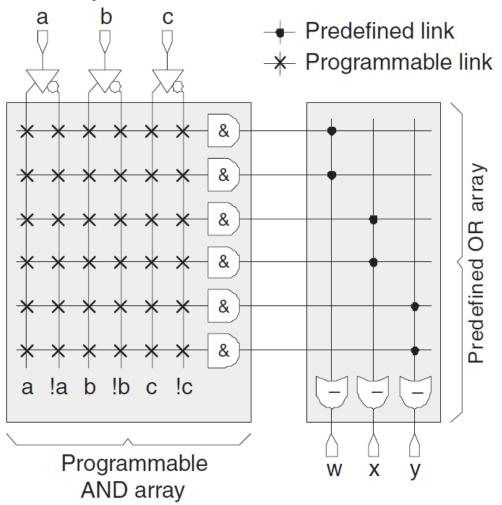

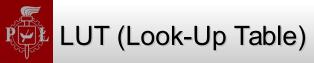

- Programmable (Field Programmable Logic Devices)

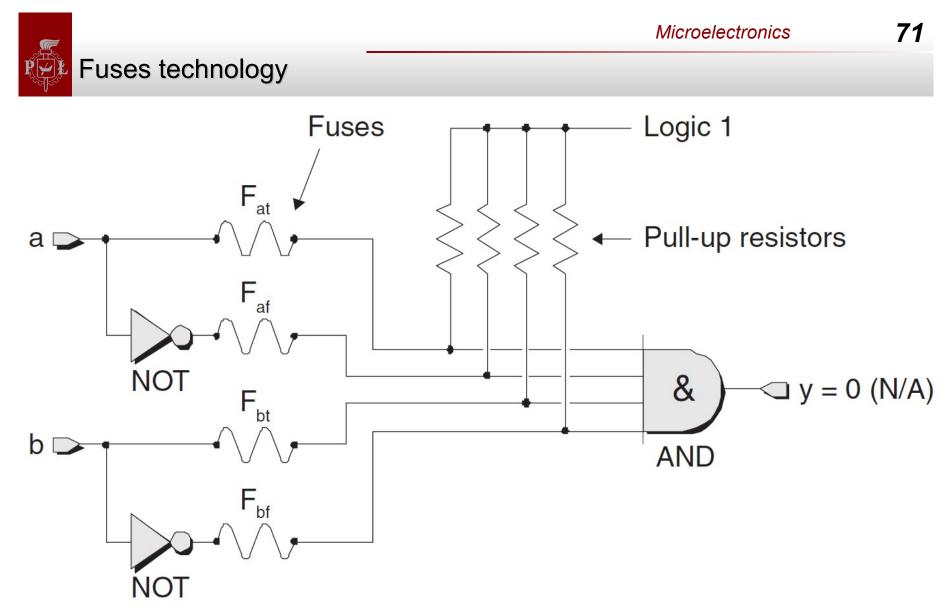

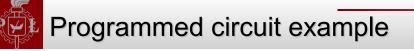

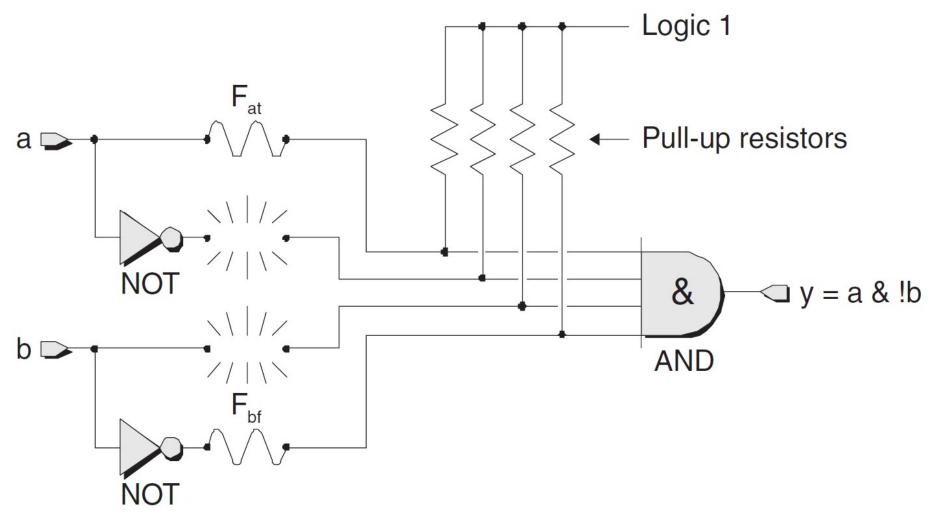

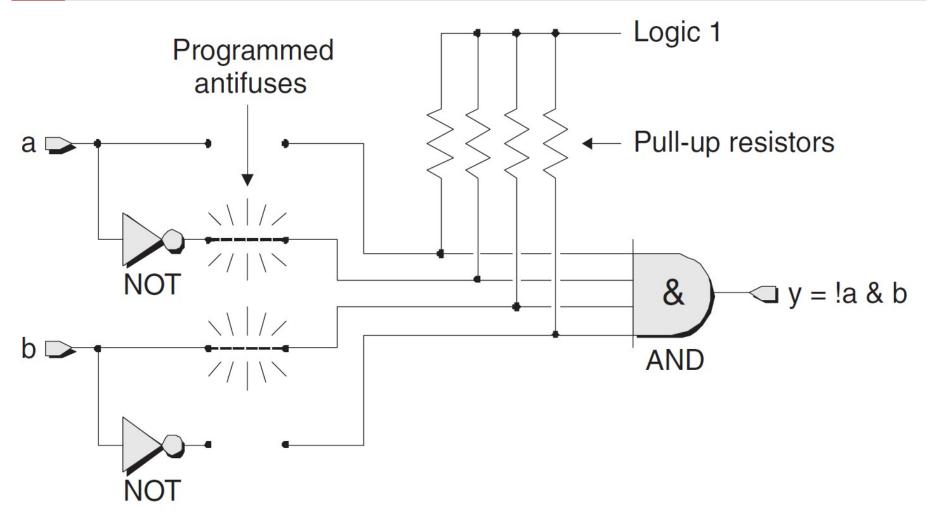

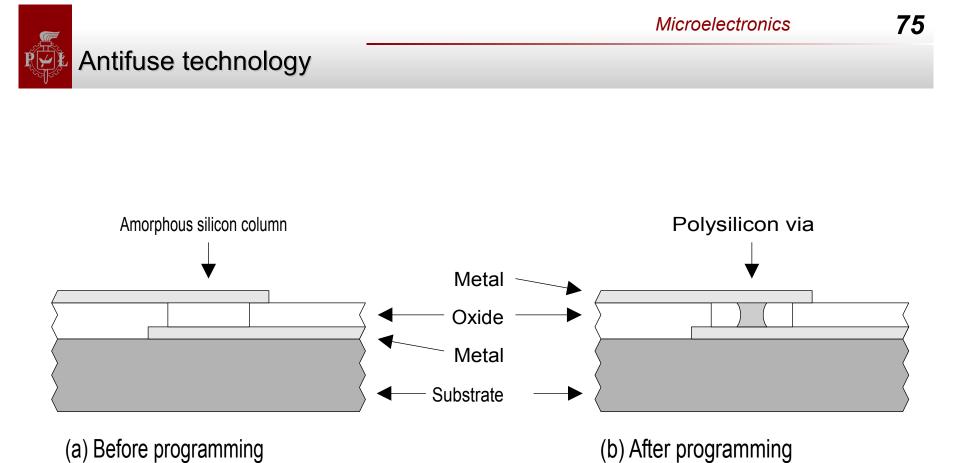

- Writable (Laser, Fuse, Antifuse, OTP EPROM)

- Writable/erasable (EPROM, EEPROM, Flash memory, Ferroelectric)

- Volatile (SRAM, FPGA)

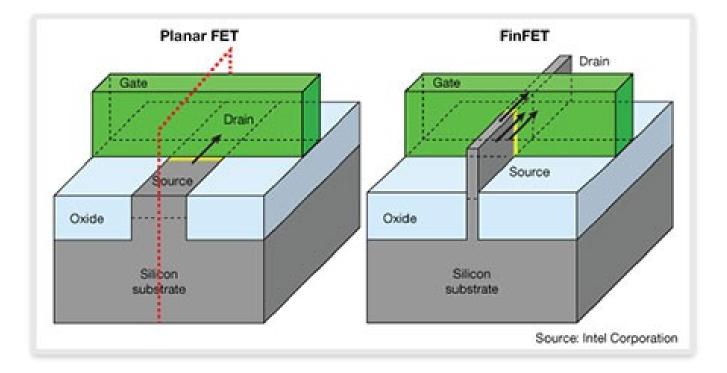

### The MOS transistor

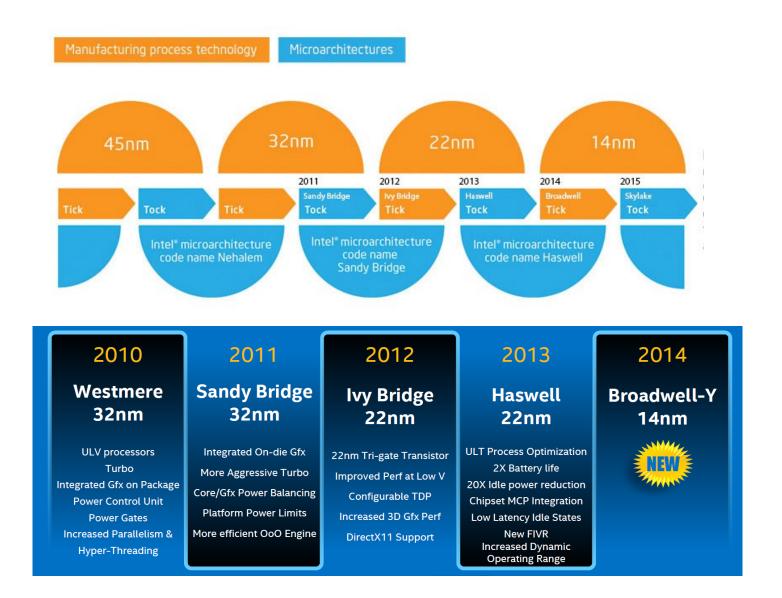

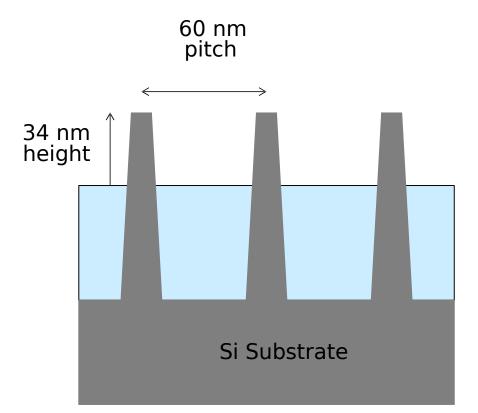

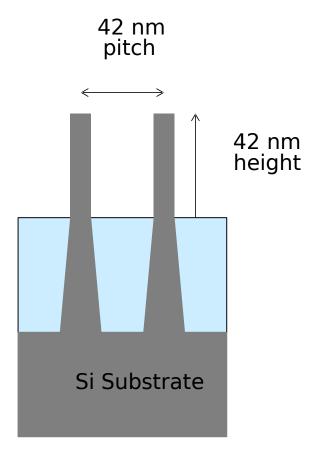

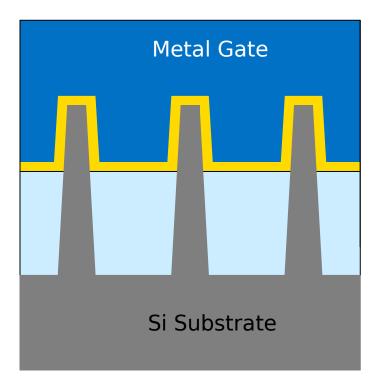

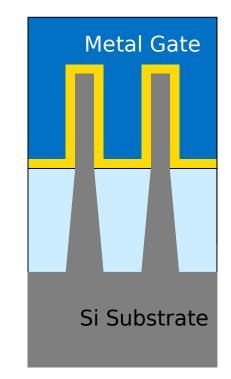

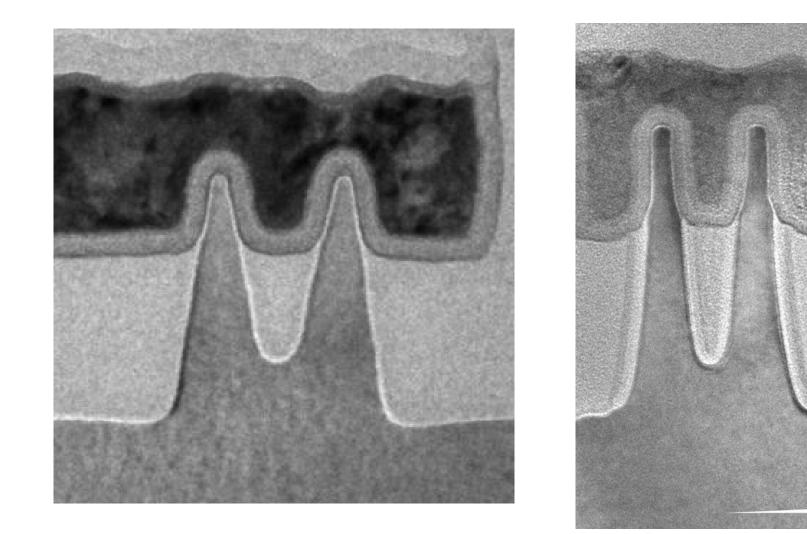

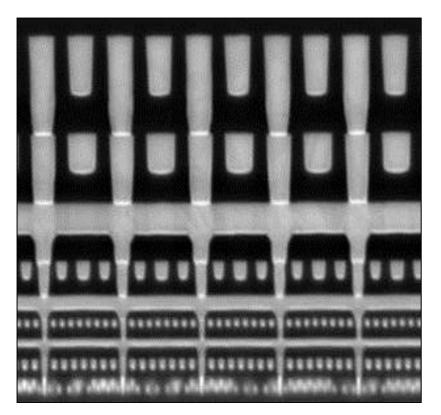

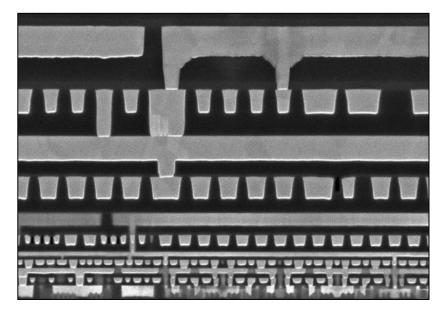

### 22 nm Process

14 nm Process

#### Transistor Fin Improvement

### 22 nm Process

# 80 nm minimum pitch

### 14 nm Process

*Microelectronics*

### 52 nm minimum pitch

### 22 nm Process

# 14 nm Process

# .108 um<sup>2</sup>

.0588 um<sup>2</sup>

(Used on CPU products)

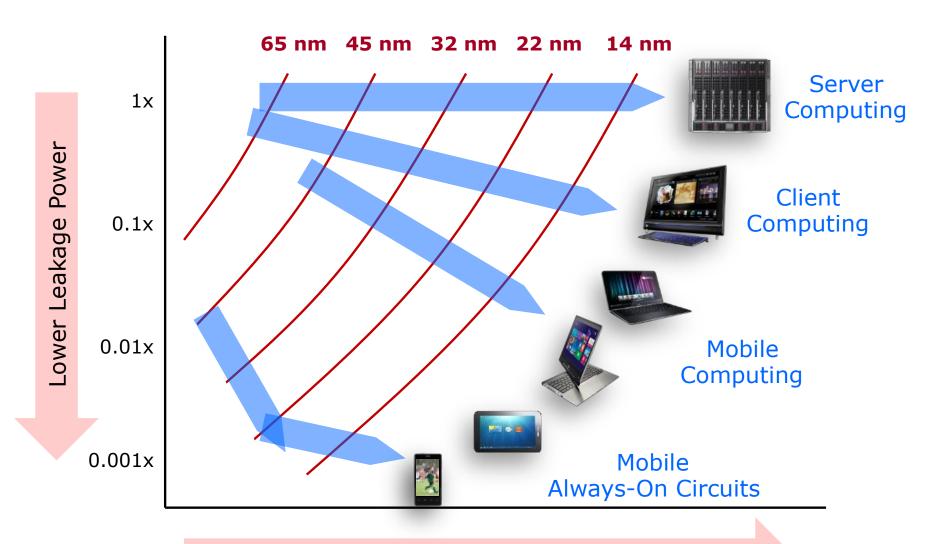

#### Transistor Performance vs. Leakage

Higher Transistor Performance (switching speed)

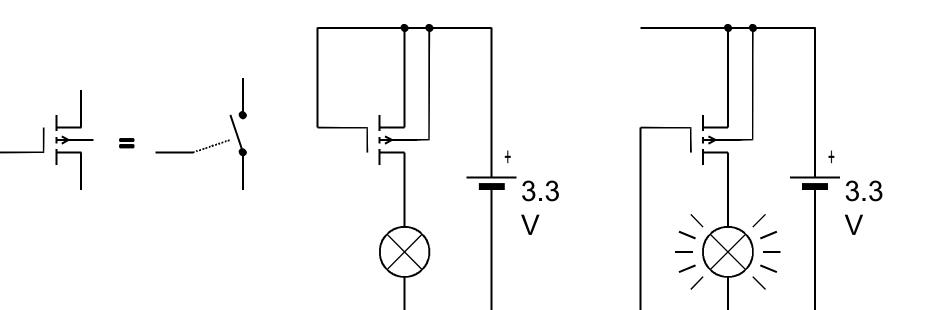

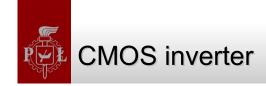

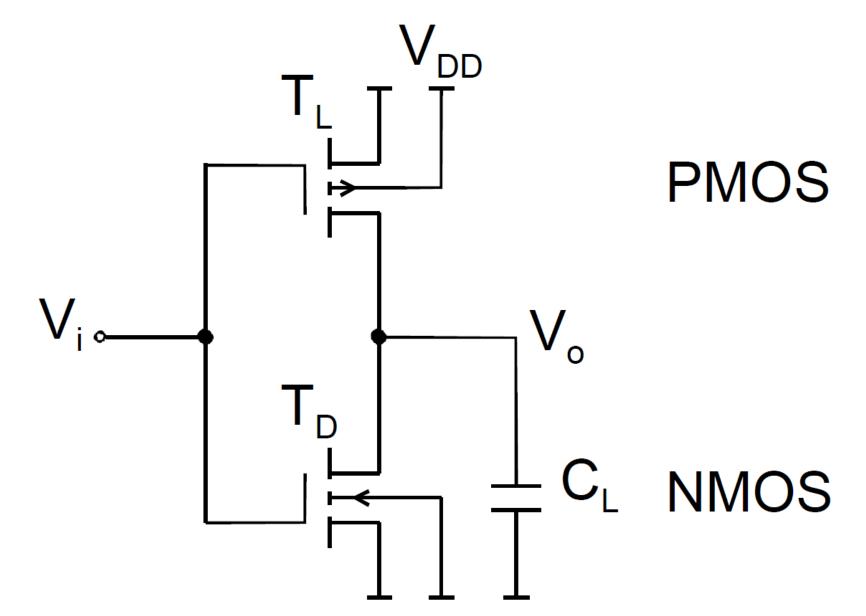

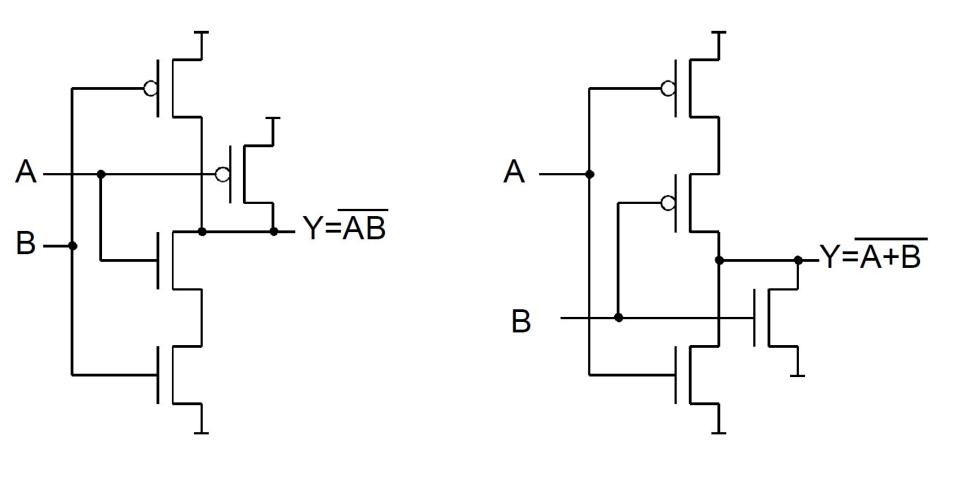

#### CMOS gates: NAND and NOR

a)

67

Source: Maxfield C., "The Design Warrior's Guide to FPGAs"

Source: Maxfield C., "The Design Warrior's Guide to FPGAs"

Source: Maxfield C., "The Design Warrior's Guide to FPGAs"

Source: Maxfield C., "The Design Warrior's Guide to FPGAs"

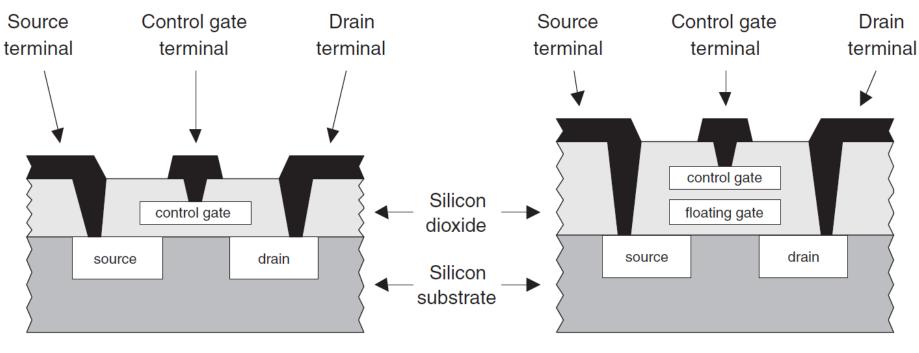

### EPROM (Eraseable Programmable ROM)

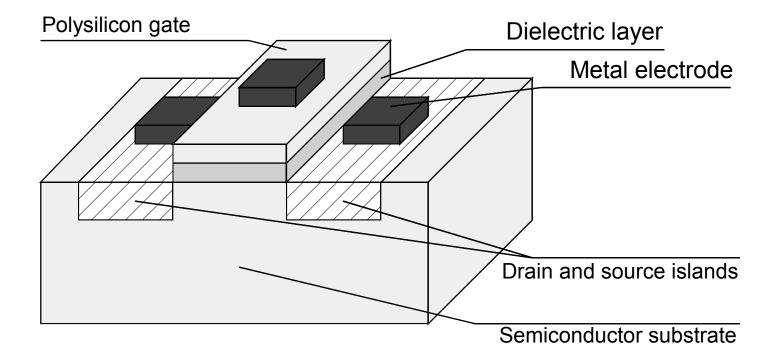

(a) Standard MOS transistor

(b) EPROM transistor

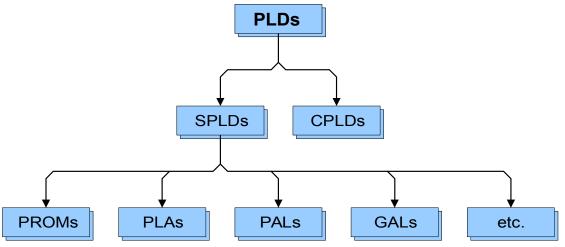

#### PLD (Programmable Logic Devices)

- First programmable logic devices were called PLD

- PLDs can be divided into two groups:

- SPLDs : Simple PLDs

- CPLDs: Complex PLDs

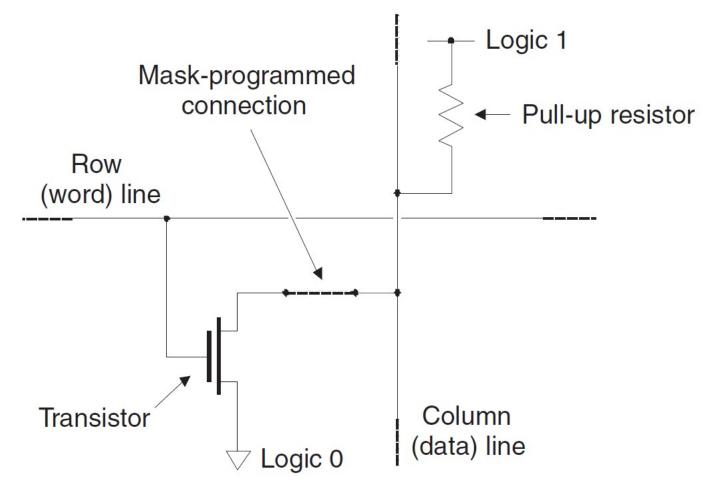

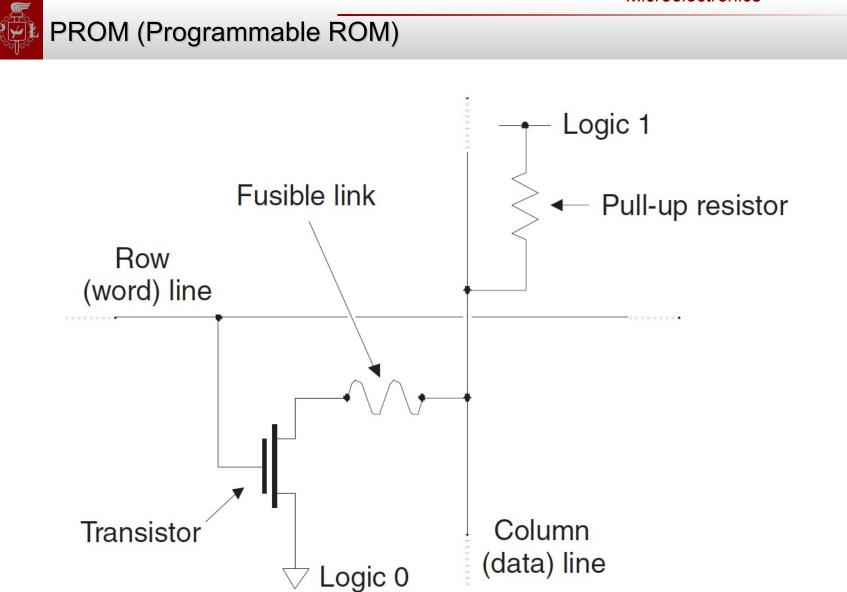

- The first programmable circuit (PROM) manufactured in 70-s

- CPLD late 70-s and early 80-s

Source: Maxfield C., "The Design Warrior's Guide to FPGAs"

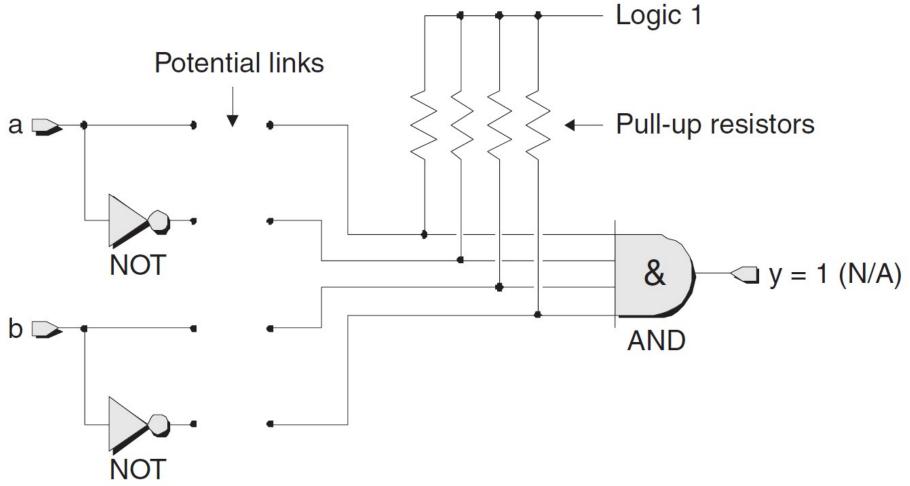

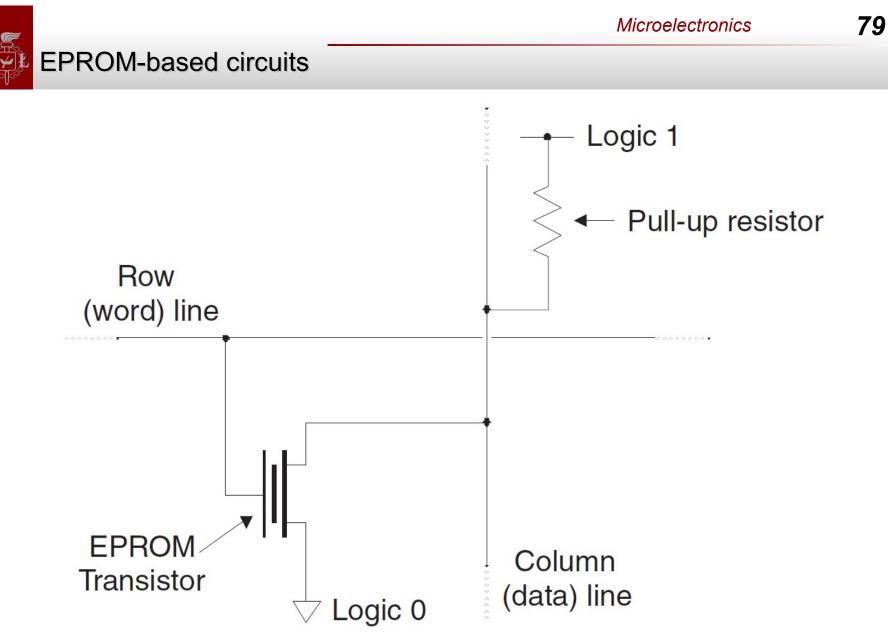

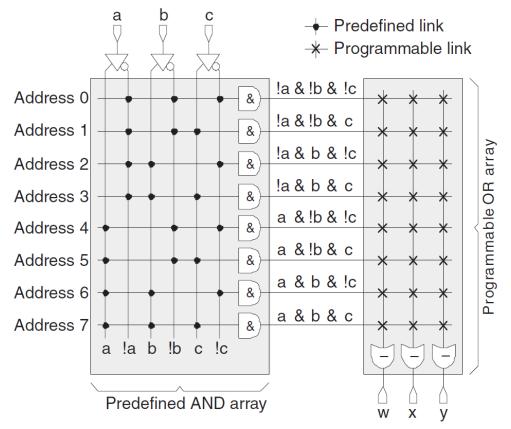

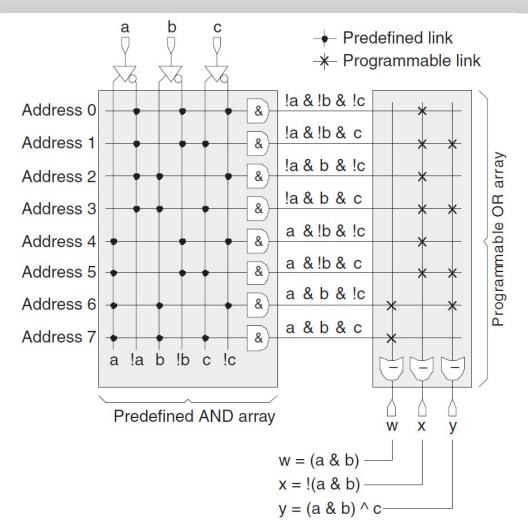

- The simplest Programmable Logic Device

- Predefined AND matrix, programmable OR matrix

#### **Programmed PROM**

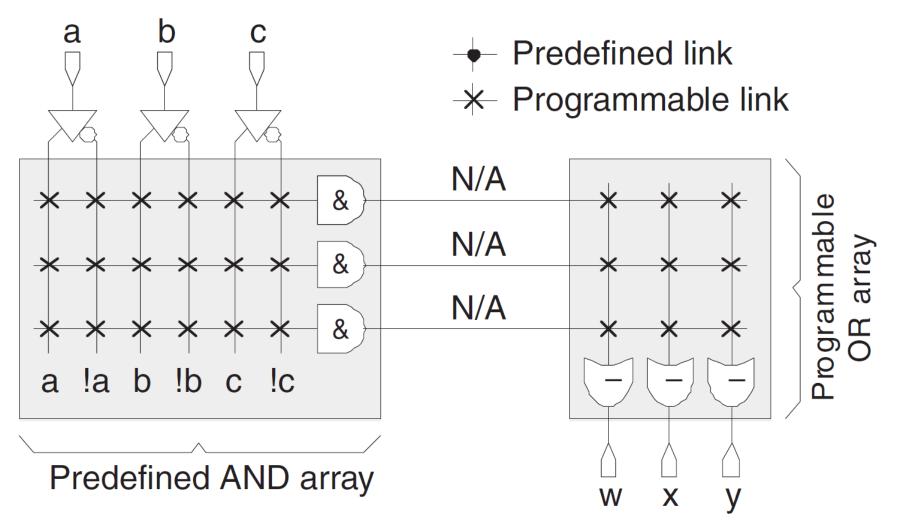

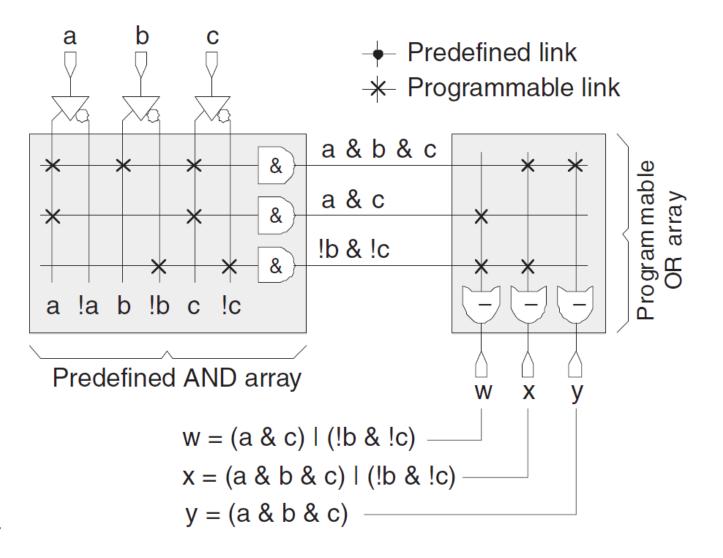

#### PLA (Programmable Logic Array)

- Complementary to PROM

- Programmable AND matrix, predefined OR matrix

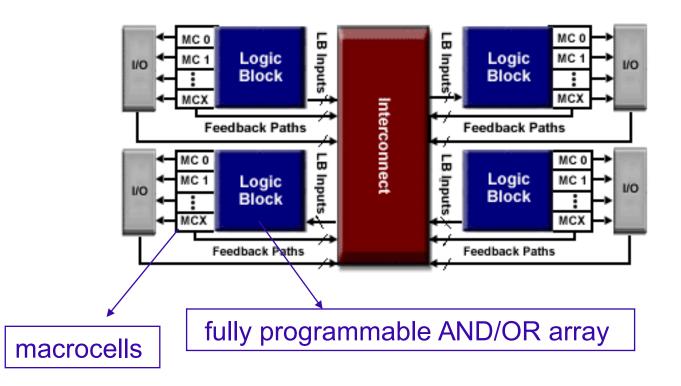

#### **Complex Programmable Logic Devices**

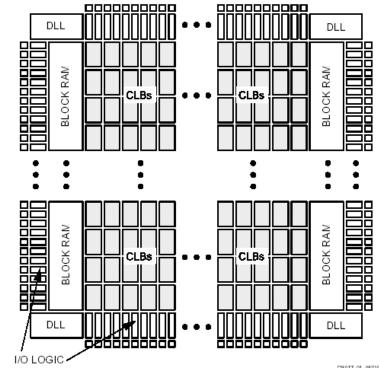

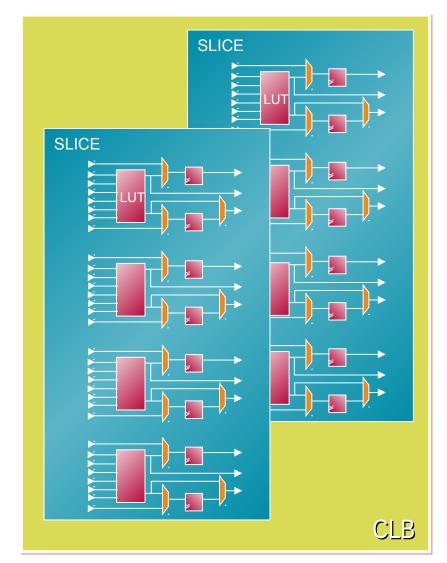

- Three main components:

- Configurable Logic Blocks (CLB)

- Programmable input/output blocks

- Programmable connections

87

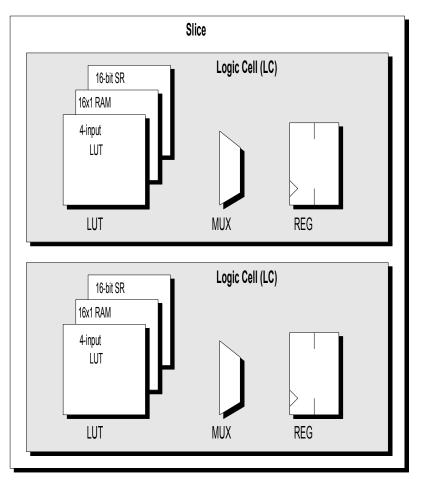

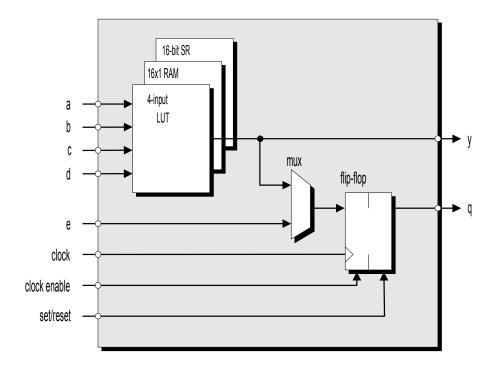

# • Every slice contains two logic cells

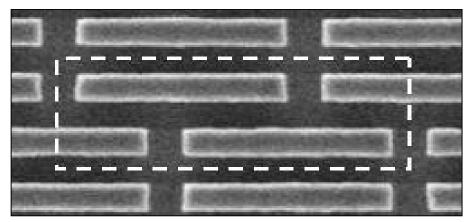

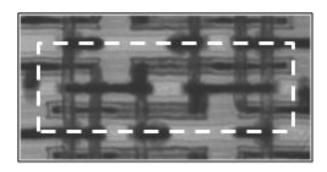

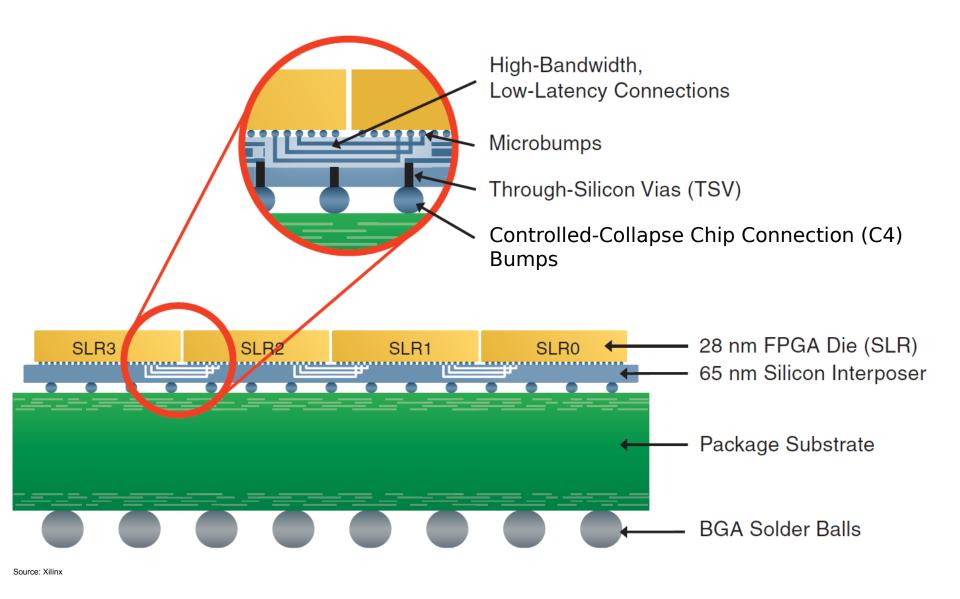

#### Stacked Silicon Interconnect technology

#### Leading FPGA Manufacturers

- Giants

- Xilinx Inc., 47% market share in 2012

- Altera Corp., 41% market share in 2012

- Niche players

- Lattice Semiconductor Corp.

- Microsemi (Actel)

- QuickLogic Corp.

- Legacy devices

- Atmel

- Cypress

- Startups

- Tabula

- Achronix

- SiliconBlue

• Main products: FPGA circuits and design software

- The company does not own a silicon foundry (fabless company)

- Manufactures its chips in the factories of:

- UMC (Taiwan)

- Xilinx owns UMC shares since 1996

- Seiko Epson (Japan)

- TSMC (Taiwan)

## Xilinx FPGA families

- High-performance families

- Virtex (220 nm)

- Virtex-E, Virtex-EM (180 nm)

- Virtex-II (130 nm)

- Virtex-II PRO (130 nm)

- Virtex-4 (90 nm)

- Virtex-5 (65 nm)

- Virtex-6 (40 nm)

- Virtex-7 (28 nm)

- Low Cost Family

- Spartan/XL derived from XC4000

- Spartan-II derived from Virtex

- Spartan-IIE derived from Virtex-E

- Spartan-3 (90 nm)

- Spartan-3E (90 nm) logic optimized

- Spartan-3A (90 nm) I/O optimized

- Spartan-3AN (90 nm) non-volatile,

- Spartan-3A DSP (90 nm) DSP optimized

- Spartan-6 (45 nm)

- Artix-7 (28 nm)

|                            | ARTIX.7                  | KINTEX.                              | VIRTEX.7                                 |

|----------------------------|--------------------------|--------------------------------------|------------------------------------------|

| Maximum Capability         | Lowest Power<br>and Cost | Industry's Best<br>Price/Performance | Industry's Highest<br>System Performance |

| Logic Cells                | 20K – 355K               | 70K – 480K                           | 285K – 2,000K                            |

| Block RAM                  | 12 Mb                    | 34 Mb                                | 65 Mb                                    |

| DSP Slices                 | 40 – 700                 | 240 – 1,920                          | 700 – 3,960                              |

| Peak DSP Perf.             | 504 GMACS                | 2,450 GMACs                          | 5,053 GMACS                              |

| Transceivers               | 4                        | 32                                   | 88                                       |

| Transceiver<br>Performance | 3.75Gbps                 | 6.6Gbps and 12.5Gbps                 | 12.5Gbps,<br>13.1Gbps and 28Gbps         |

| Memory Performance         | 1066Mbps                 | 1866Mbps                             | 1866Mbps                                 |

| I/O Pins                   | 450                      | 500                                  | 1,200                                    |

| I/O Voltages               | 3.3V and below           | 3.3V and below<br>1.8V and below     | 3.3V and below<br>1.8V and below         |

#### Xilinx 7-series CLB Structure

- Two side-by-side slices per CLB

- Slice\_M are memory-capable

- Slice\_L are logic and carry only

- Four 6-input LUTs per slice

Single LUT in Slice\_M can be a 32-bit shift register or 64 x 1 RAM

- Two flip-flops per LUT

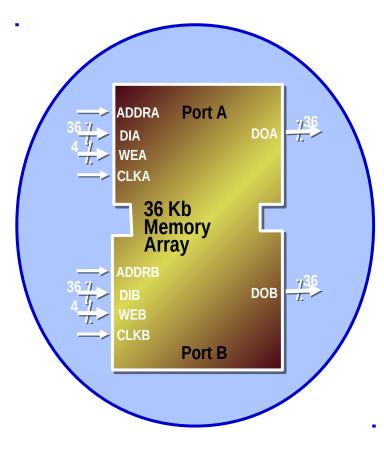

- 36K/18K block RAM

- 32k x 1 to 512 x 72 in one 36K block

- Simple dual-port and true dual-port configurations

- Built-in FIFO logic

- 64-bit error correction coding per 36K block

- Adjacent blocks combine to 64K x 1 without extra logic

- Available in all families

- GTP transceivers up to 3.75 Gbps

- Ultra high volume transceiver

- Wire bond package capable

- GTX transceivers up to 12.5 Gbps

Support for the most common 10 Gbps protocols

- GTH transceivers up to 13.1 Gbps

Support for 10 Gbps protocols with high FEC

- overhead

- GTZ transceivers up to 28 Gbps

- Enables next generation 100–400Gbps system line cards

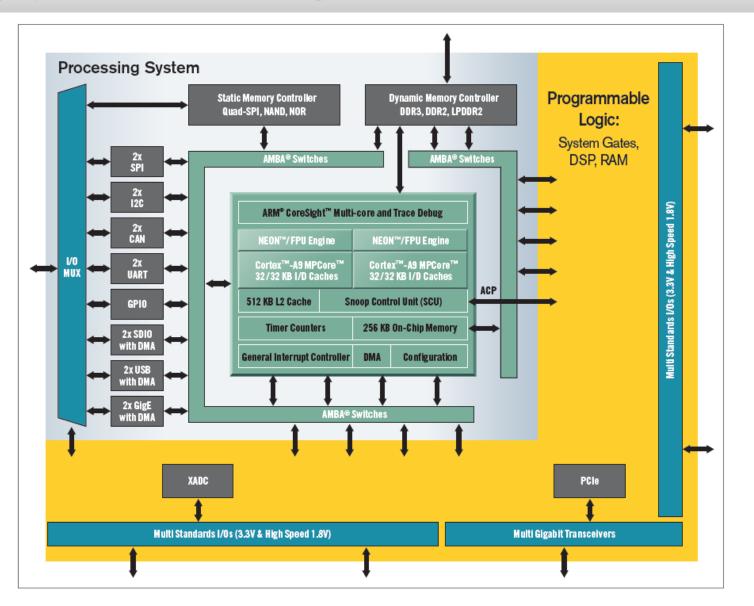

#### Zynq - Extensible Processing Platform

#### Zynq-7000 Product Table (Software View)

| Device Name                                                                                       | Z-7010                                                                                                                                | Z-7020                  | Z-7030                   | Z-7045                   |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------|--------------------------|--|

| Part Number                                                                                       | XC7Z010                                                                                                                               | XC7Z020                 | XC7Z030                  | XC7Z045                  |  |

| Processor Core                                                                                    | Dual ARM <sup>®</sup> Cortex™-A9 MPCore™ with CoreSight™                                                                              |                         |                          |                          |  |

| Processor Extensions                                                                              | NEON™ and Single/Double Precision Floating Point                                                                                      |                         |                          |                          |  |

| Maximum Frequency                                                                                 | 800 MHz                                                                                                                               |                         |                          |                          |  |

| L1 Cache                                                                                          | 32 KB Instruction, 32 KB Data per processor                                                                                           |                         |                          |                          |  |

| L2 Cache                                                                                          | 512 KB                                                                                                                                |                         |                          |                          |  |

| On-Chip Memory                                                                                    | 256 KB                                                                                                                                |                         |                          |                          |  |

| External Memory Support                                                                           | DDR3, DDR2, LPDDR2                                                                                                                    |                         |                          |                          |  |

| External Static Memory Support                                                                    | 2x QSPI-SPI, NAND, NOR                                                                                                                |                         |                          |                          |  |

| DMA Channels                                                                                      | 8 (4 dedicated to Programmable Logic)                                                                                                 |                         |                          |                          |  |

| Peripherals                                                                                       | 2x USB 2.0 (OTG) w/DMA, 2x Tri-mode Gigabit Ethernet w/DMA, 2x SD/SDIO w/DMA,<br>2x UART (2), 2x CAN2.0B, 2x I2C, 2x SPI, 4x 32b GPIO |                         |                          |                          |  |

| Security                                                                                          | AES and SHA 256b for secure boot                                                                                                      |                         |                          |                          |  |

| Peripherals and Static Memory Multiplexed I/O <sup>(1)</sup>                                      | 54                                                                                                                                    |                         |                          |                          |  |

| Processing System to Programmable Logic Interface Ports<br>(Primary Interfaces & Interrupts Only) | 2x AXI 32b Master, 2x AXI 32b Slave,<br>4x AXI 64b/32b Memory<br>AXI 64b ACP<br>16 Interrupts                                         |                         |                          |                          |  |

| Xilinx 7 Series Programmable Logic Equivalent                                                     | Artix™-7 FPGA                                                                                                                         | Artix™-7 FPGA           | Kintex™-7 FPGA           | Kintex™-7 FPGA           |  |

| Programmable Logic Cells (Approximate ASIC Gates <sup>(3)</sup> )                                 | 28K Logic Cells (~430K)                                                                                                               | 85K Logic Cells (~1.3M) | 125K Logic Cells (~1.9M) | 350K Logic Cells (~5.2M) |  |

| Extensible Block RAM (# 36 Kb Blocks)                                                             | 240KB (60)                                                                                                                            | 560KB (140)             | 1,060KB (265)            | 2,180KB (545)            |  |

| Programmable DSP Slices (18x25 MACCs)                                                             | 80                                                                                                                                    | 220                     | 400                      | 900                      |  |

| Peak DSP Performance (Symmetric FIR)                                                              | 58 GMACS                                                                                                                              | 158 GMACS               | 480 GMACS                | 1080 GMACS               |  |

| PCI Express <sup>®</sup> (Root Complex or Endpoint)                                               | -                                                                                                                                     | -                       | Gen2 x4                  | Gen2 x8                  |  |

| Agile Mixed Signal (AMS)/XADC                                                                     | 2x 12 bit, 1 MSPS ADCs with up to 17 Differential Inputs                                                                              |                         |                          |                          |  |

| Security                                                                                          | AES and SHA 256b for secure configuration                                                                                             |                         |                          |                          |  |

| Multi-Standards 3.3V I/O <sup>(2)</sup>                                                           | 100                                                                                                                                   | 200                     | 250                      | 350                      |  |

| Serial Transceivers <sup>(2)</sup>                                                                | -                                                                                                                                     | -                       | 4                        | 16                       |  |

|                                                                                                   |                                                                                                                                       |                         |                          |                          |  |

- ASIC Advantages

- Optimized for a specific application

- Effective area consumption

- Higher performance (because of replacing a few circuits by one)

- ASIC Disadvantages

- Higher cost

- Development cost paid by the user

- Single supplier

- Need for own specialists in IC design

- Long development cycle

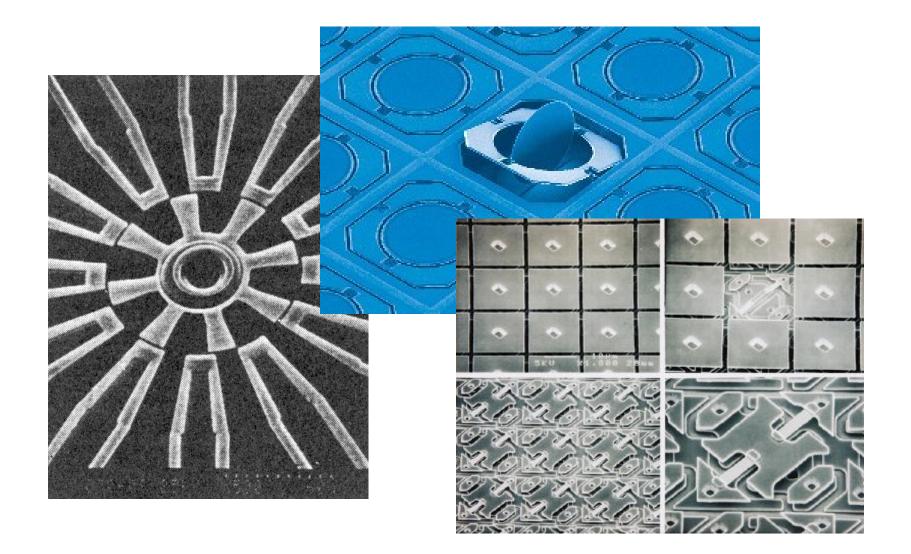

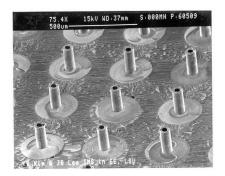

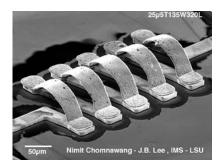

## The 90's – MEMS (Micro Electro-Mechanical Systems)

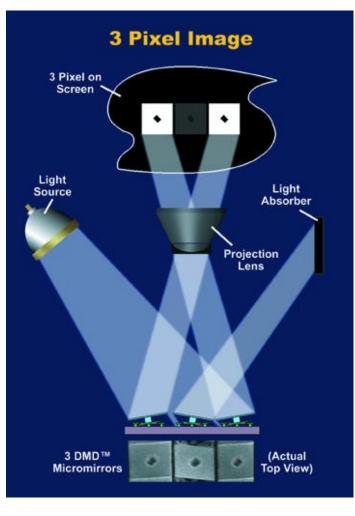

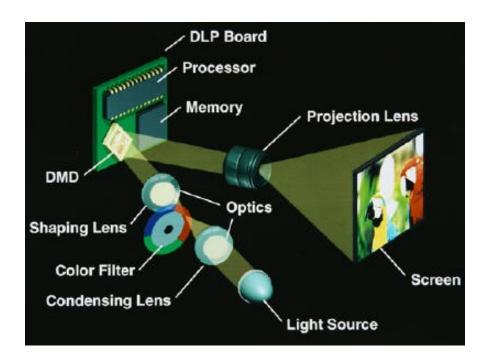

#### MEMS Application – Projection TV

102

- Automotive sensors

- Accelerometers, force/torque sensors, pressure sensors

- Bio MEMS

- Micro total analysis system (µTAS), DNA sequencing chips, clinical diagnostics, drug delivery systems

- Chemistry

- Lab-on-a-chip, microreactor

- Optics

- Digital micromirror devices (TI), grating light valve (GLV)

- Optical interconnects, switching

- Data storage

- Precision servo, shock sensors for HDD, new data storage mechanisms

- RF, microwave for communication

- Power generation

- Micromachined turbine engines, MEMS power generators

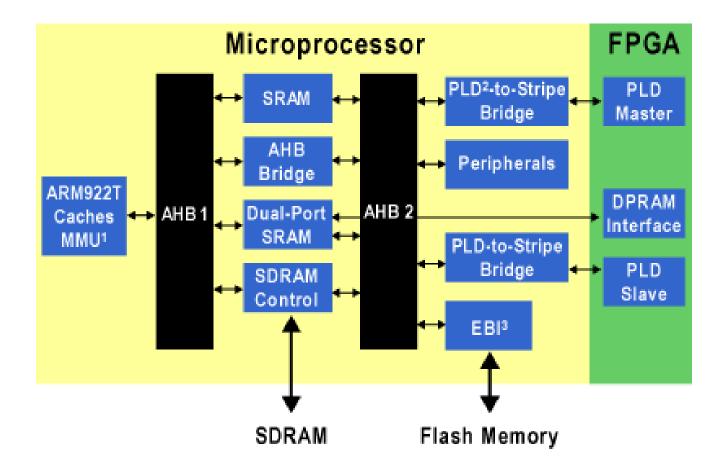

- Processor core with external hardware (network, USB, PCI interface ...) on the same chip

- Intelectual property (IP) -based design

- Design reuse

- Hardware-software co-design

- Custom or FPGA-based

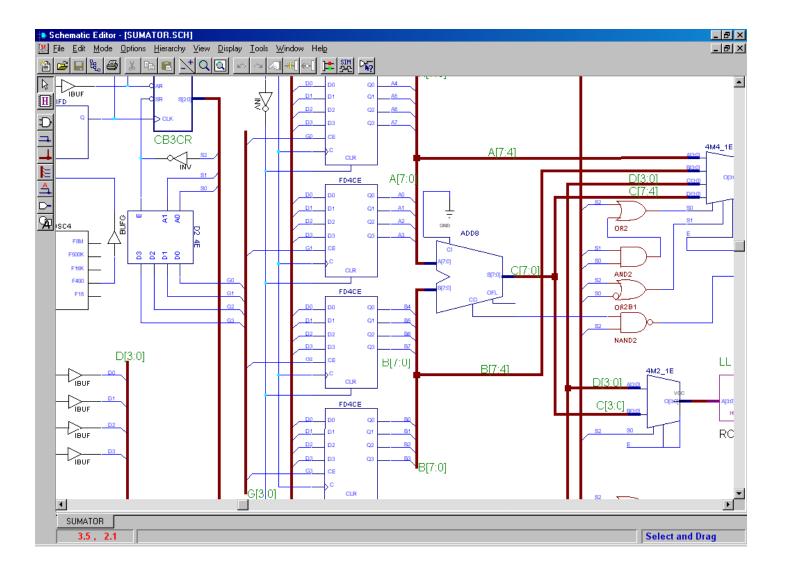

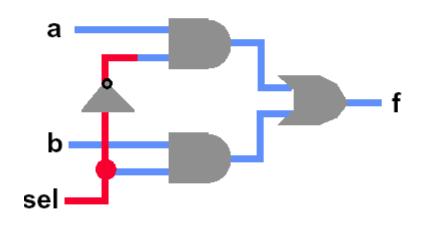

- Draw the schematic

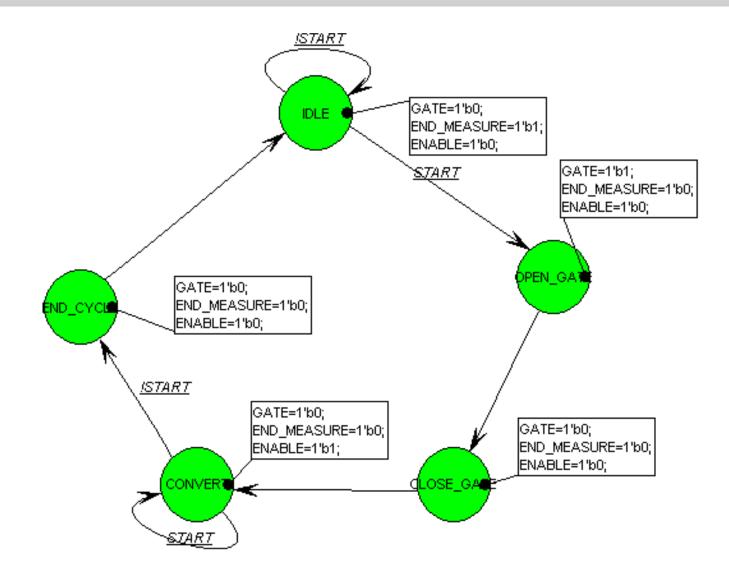

- Draw the state diagram

- Describe in Hardware Description Language, e.g. VHDL\* or Verilog

- Draw the masks

\*VHDL - Very High Speed Integrated Circuits Hardware Description Language

#### **Draw The Schematic**

Py)

108

## Describe in Hardware Description Language

| output       | c (f, a, b, sel);<br>f;<br>a, b, sel; |  |  |

|--------------|---------------------------------------|--|--|

| and #5       | g1 (f1, a, nsel),<br>g2 (f2, b, sel); |  |  |

| or #5<br>not | g3 (f, f1, f2);<br>g4 (nsel, sel);    |  |  |

| endmodule    | g (11001, 001),                       |  |  |

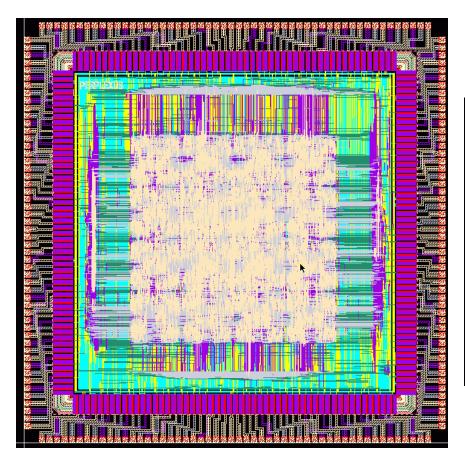

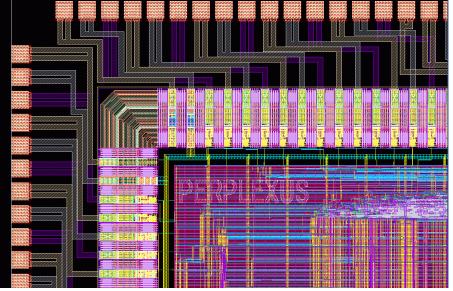

#### **Draw The Masks**

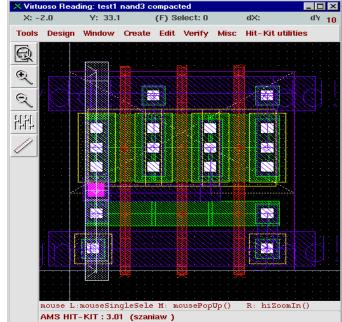

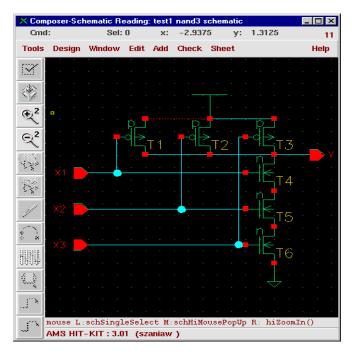

#### Masks and Schematic in Cadence

- Synopsys

- Cadence

- Mentor Graphics

### Functions of the Design Tools

- Edition of text, schematic, layout

- Logic synthesis

- Layout versus Schematic (LVS)

- Design/Electrical Rule Checking (DRC/ERC)

- Place and Route

- Simulation

- Programmable circuits

- EUROPRACTICE

- IET Experimental Line

- Western/Far East Silicon Foundries