# Yield, Reliability and Testing

# The Progressive Trend of IC Technology

| Integration level | Year  | Number of transistors             | DRAM integration |

|-------------------|-------|-----------------------------------|------------------|

| SSI               | 1950s | less than 10 <sup>2</sup>         |                  |

| MSI               | 1960s | 10 <sup>2</sup> - 10 <sup>3</sup> |                  |

| LSI               | 1970s | 10 <sup>3</sup> - 10 <sup>5</sup> | 4K, 16K, 64K     |

| VLSI              | 1980s | 10 <sup>5</sup> - 10 <sup>7</sup> | 256K, 1M, 4M     |

| ULSI              | 1990s | 10 <sup>7</sup> - 10 <sup>9</sup> | 16M. 64M, 256M   |

| SLSI              | 2000s | over 10 <sup>9</sup>              | 1G, 4G and above |

## **Costs of Fault Detection**

| Production stage  | Cost of detected fault     |

|-------------------|----------------------------|

| Die               | US\$ 0,01 - US\$ 0,10      |

| Packaged IC       | US\$ 0,10 - US\$ 1,00      |

| PCB               | US\$ 1,00 - US\$ 10,00     |

| Electronic system | US\$ 10,00 - US\$ 100,00   |

| Shipped product   | US\$ 100,00 - US\$ 1000,00 |

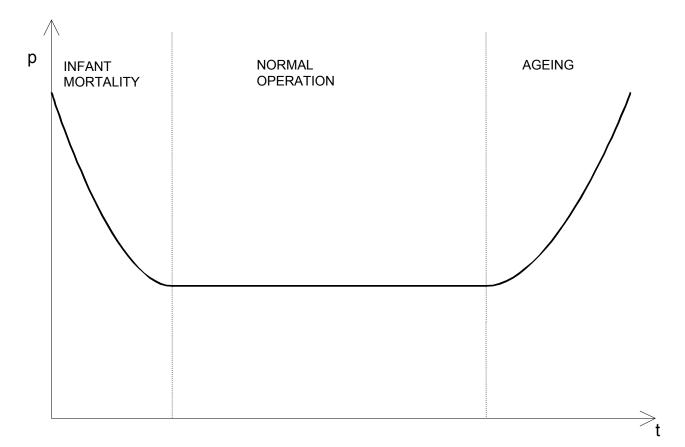

## **Failure Rate During Product Life**

## **Failure Mechanisms**

- Stress failures

- Electrical Overstress (EOS)

- Electrostatic Discharge (ESD)

- Intrinsic failures

- Crystal defects, processing defects, gate oxide breakdown, ionic contamination etc.

- Extrinsic failures

- Packaging, metallization, bonding, attachment, radiation

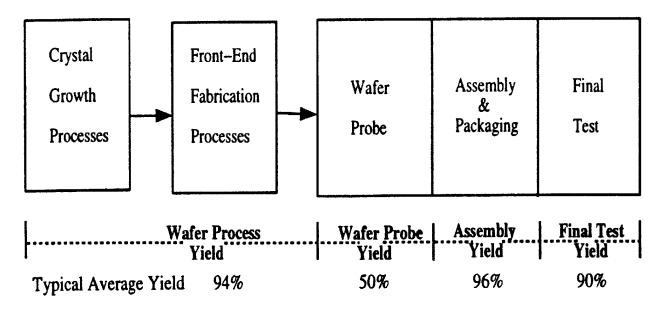

# Yield

Yield =  $\frac{\text{Number of working devices}}{\text{Number of manufactured devices}}$

$$Y = Y_1 \cdot Y_2 \cdot \ldots \cdot Y_n$$

## **Some Yield Examples**

| Product                      | 4M DRAM             | 16M DRAM             | 16M DRAM            | Pentium P54C        |

|------------------------------|---------------------|----------------------|---------------------|---------------------|

| Feature size                 | 0.6μ                | 0.5μ                 | <b>0.35</b> μ       | 0.6μ                |

| Wafer size                   | 150mm               | 200mm                | 200mm               | 200mm               |

| Tested wafer cost            | \$600               | \$1,140              | \$1,410             | \$1,500             |

| Die size                     | 54.8mm <sup>2</sup> | 116.1mm <sup>2</sup> | 100mm <sup>2</sup>  | 163mm <sup>2</sup>  |

| Total dice available / wafer | 254                 | 212                  | 253                 | 148                 |

| Defect density               | 0.5/cm <sup>2</sup> | 1.0/cm <sup>2</sup>  | 0.6/cm <sup>2</sup> | 1.5/cm <sup>2</sup> |

| Probe yieid                  | 80%                 | 35%                  | 58%                 | 15%                 |

| Number of good dice          | 203                 | 74                   | 146                 | 22                  |

| Factory cost /die            | \$4.14              | \$23.25              | \$12.63             | \$153.31            |

| Average selling price / die  | \$12                | \$60                 | \$27                | \$700               |

| Approx. revenue/wafer start  | \$2,140             | \$3,120              | \$3,430             | \$11,200            |

| Revenue/sq. in. started      | \$70                | \$62                 | \$68                | \$223               |

| Gross margin                 | 65%                 | 61%                  | 53%                 | 78%                 |

## **Testing Costs**

| Product           | Final test cost (\$) | Final test yield(%) |

|-------------------|----------------------|---------------------|

| 8-bit MPU         | 0.10                 | 95                  |

| 20,000 gate array | 0.80                 | 90                  |

| 1MDRAM            | 0.30                 | 93                  |

| 4M DRAM           | 0.40                 | 90                  |

| 16M DRAM          | 0.80                 | 75                  |

| 4K GaAs SRAM      | 1.00                 | 80                  |

| 32-bit MPU (386)  | 2.50                 | 90                  |

| 32-bit MPU (P54C) | 25.00                | 75                  |

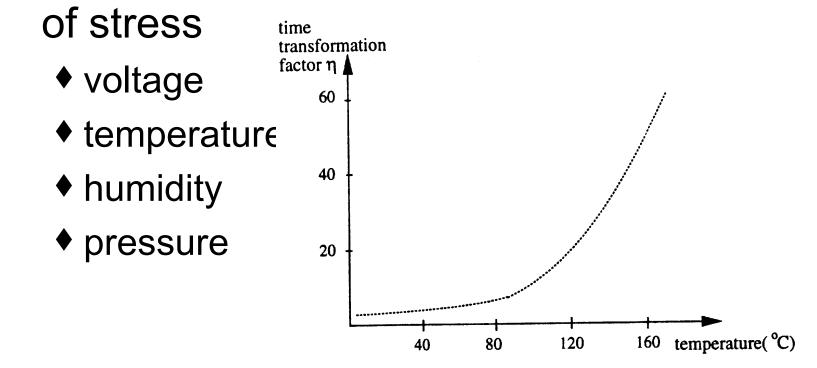

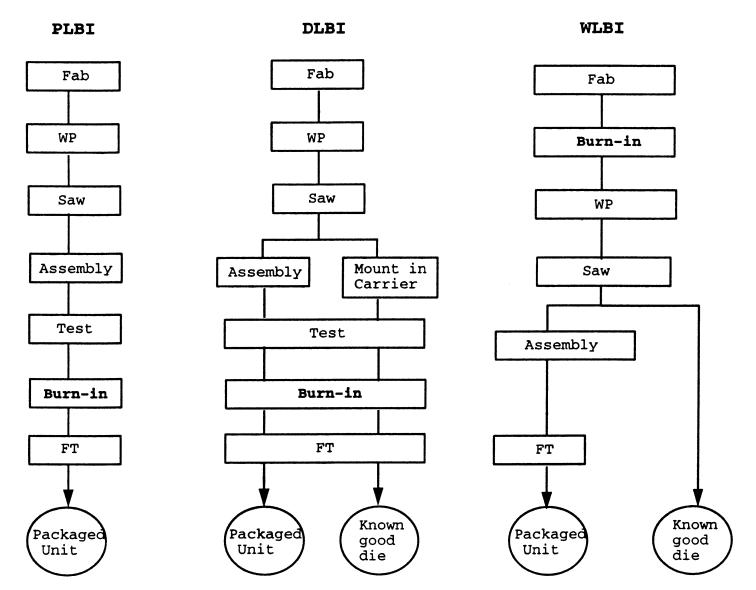

## **Burn-in**

Units subjected to higher than usual levels

## **Burn-in (contd.)**

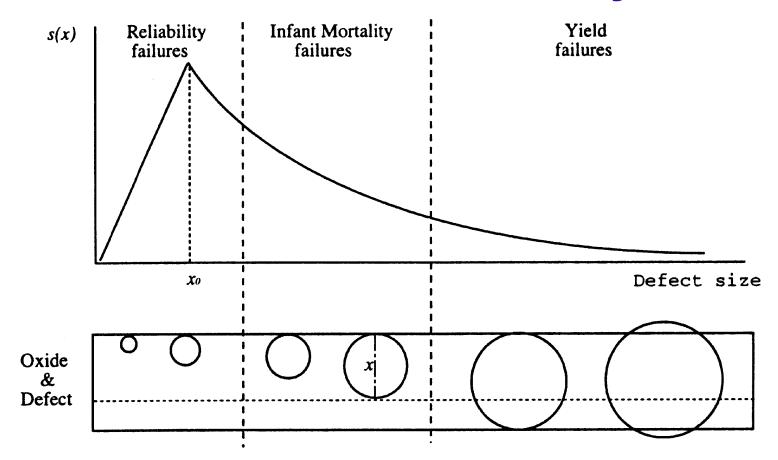

#### **Yield and Reliability**

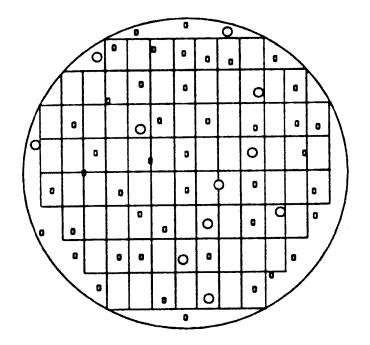

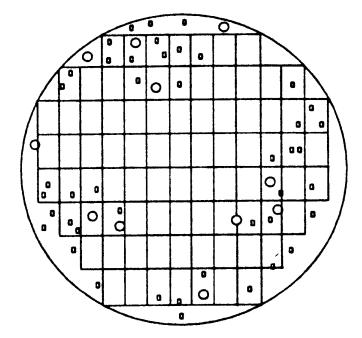

#### **Defect Clustering**

## **Reliability Measures**

- Mean Time Beetween Failures (MTBF)

- Mean Time To Failure (MTTF)

- Failures in Time (FITs),

- ♦ 1FIT=1 failure in 10<sup>9</sup> h

- To estimate FIT of the system, we add FITs of the components

## **Reliability Example (SparcStation 1)**

- Discrete components

- Microprocessor (standard part) 5 FITs

- ◆ 100 TTLs, 50 at 10 FITs, 50 at 15 FITs

- ◆ 100 RAM chips, 6 FITs

- Overall failure rate: 5+50\*10+50\*15+100\*6=1855 FITs

- With ASICs

- Microprocessor (custom) 7 FITs

- ◆ 9 ASICs, 10 FITs

- ♦ 5 SIMMs, 15 FITs

- Overall failure rate: 7+9\*10+5\*15=175 FITs

## **Physical and Logical Faults**

| Fault |                                          | Logical fault     |                       |                        |  |

|-------|------------------------------------------|-------------------|-----------------------|------------------------|--|

| level | Physical fault                           | Degradation fault | Open-circuit<br>fault | Short-circuit<br>fault |  |

|       | Leakage or short between package leads   | √                 |                       | √ ·                    |  |

| Chip  | Broken, misaligned, or poor wire bonding |                   | ~                     |                        |  |

|       | Surface contamination, moisture          | ✓                 |                       |                        |  |

|       | Metal migration, stress, peeling         |                   | ✓                     | $\checkmark$           |  |

|       | Metallization (open or short)            |                   | ✓                     | $\checkmark$           |  |

|       | Contact opens                            |                   | ✓                     |                        |  |

|       | Gate to S/D junction short               | ✓                 |                       | ✓                      |  |

| Gate  | Field-oxide parasitic device             | ✓                 |                       | ✓                      |  |

|       | Gate-oxide imperfection, spiking         | ✓                 |                       | ✓                      |  |

|       | Mask misalignment                        | $\checkmark$      |                       | $\checkmark$           |  |

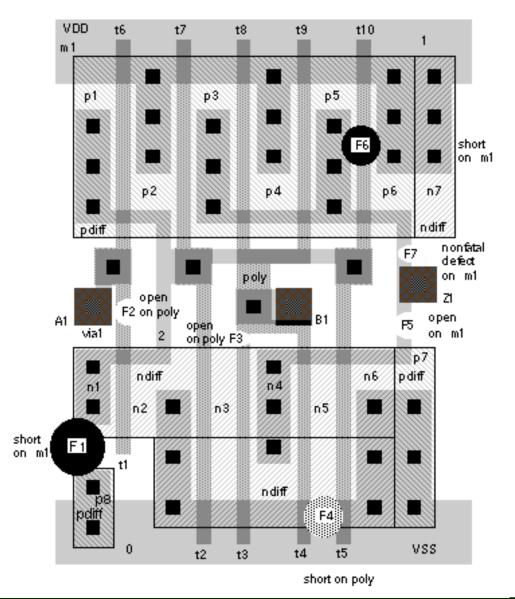

## **Defects and Physical Faults**

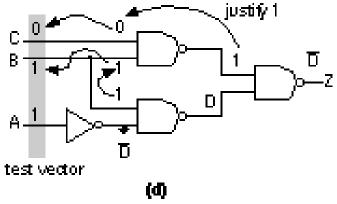

## **Logical Faults**

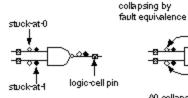

- Single stuck-at fault model

- Assuming just one fault in a tested logic

- Two kinds of logical faults

- stuck-at-0

- stuck-at-1

- Applied to the pins of logic cells (AND, OR, flipflop etc.)

- Faults propagate through the logic networks

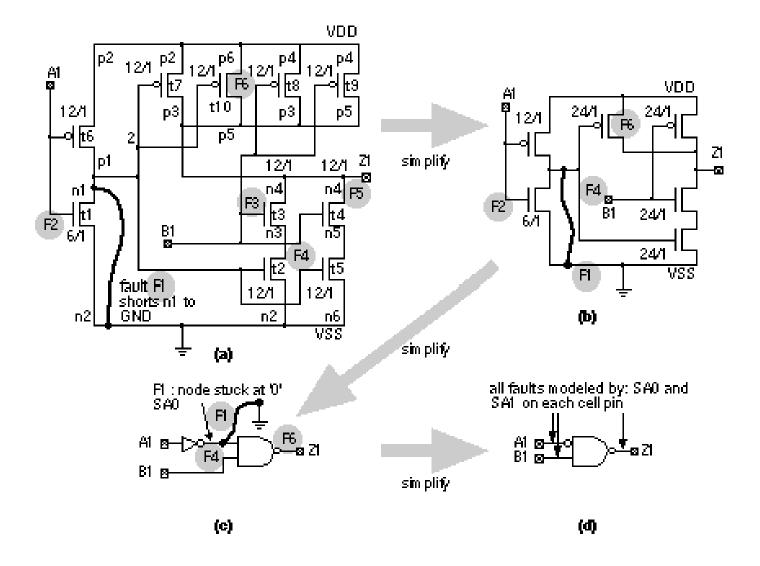

#### **Mapping Physical Faults to Logical Ones**

## **IDDQ** Testing

- Test quiescent supply current of the circuit

- Very fast and simple

- Can detect bridging faults

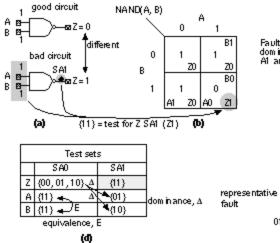

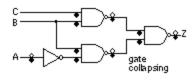

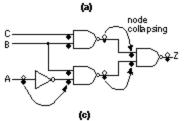

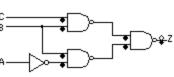

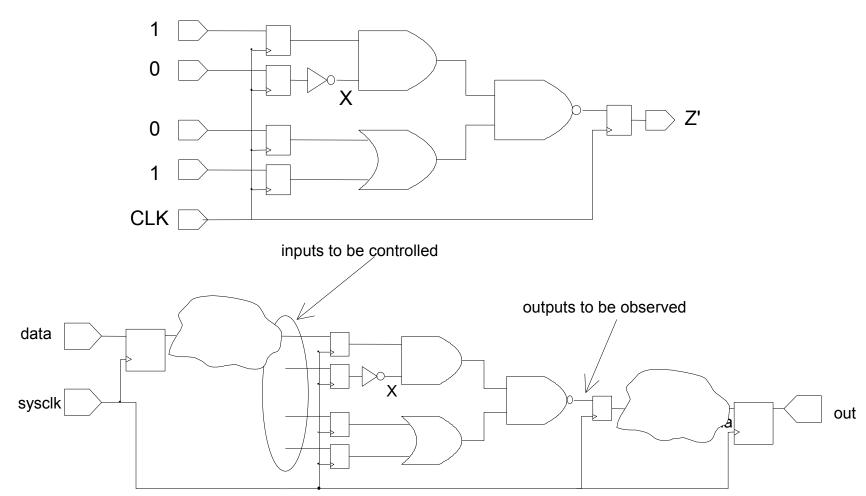

#### **Fault Collapsing**

(1)

A0 collapses to Z1 B0 collapses to Z1 (g)

20 dominates A1 and B1 A0 and B0 dominate Z1

(h)

(b) B

(đ)

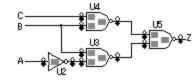

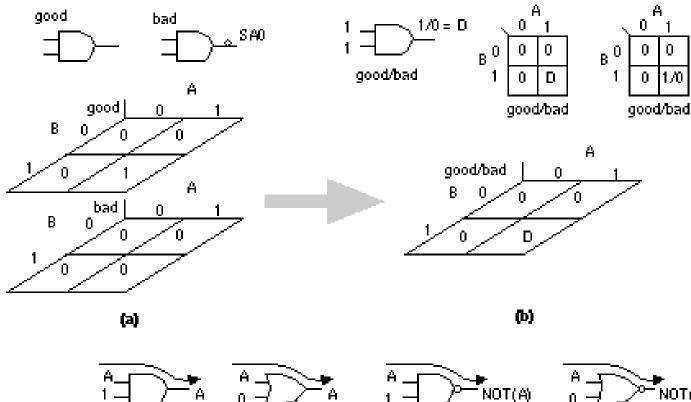

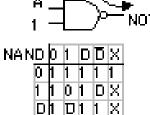

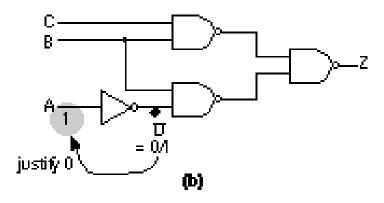

#### **Fault Propagation - D-calculus**

(c)

| Ν | D | Ū | 1 | D | D | X |  |

|---|---|---|---|---|---|---|--|

|   | 0 | Û | 0 | Ũ | 0 | Ũ |  |

|   | 1 | 0 | 1 | Û | ٥ | Х |  |

|   | D | 0 | D | Û | 0 | Х |  |

|   | ٥ | 0 | ۵ | 0 | ۵ | Х |  |

|   | Х | 0 | Х | Х | Х | Х |  |

OR 0 1 D D X ١Û. DDX 1 1 1 1 DD1 D1 X 00110X XX1 XXX

D1 DX

XXXX

Dþ

Χħ

NOT(A)

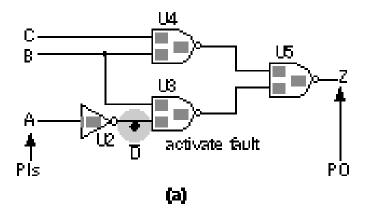

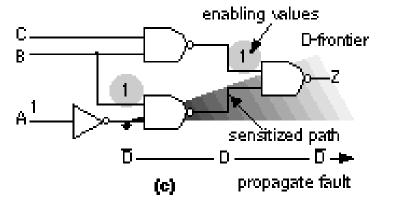

#### **Fault Propagation**

1. Choose a fault

3. (N) AND gates to 1, (N) OR gates to 0

2. Work backward

4. Work backward

### Fault Coverage

Testing by applying a set of input vectors and observing output

$FC = \frac{\text{Number of detected errors}}{\text{Number of detectable errors}}$

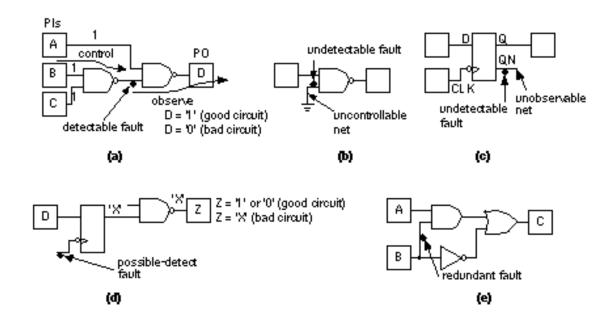

#### **Testing of Sequential Circuits**

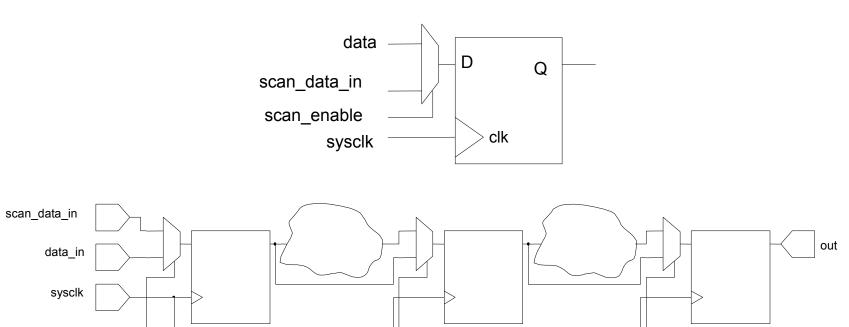

#### **Scan Path**

scan\_enable

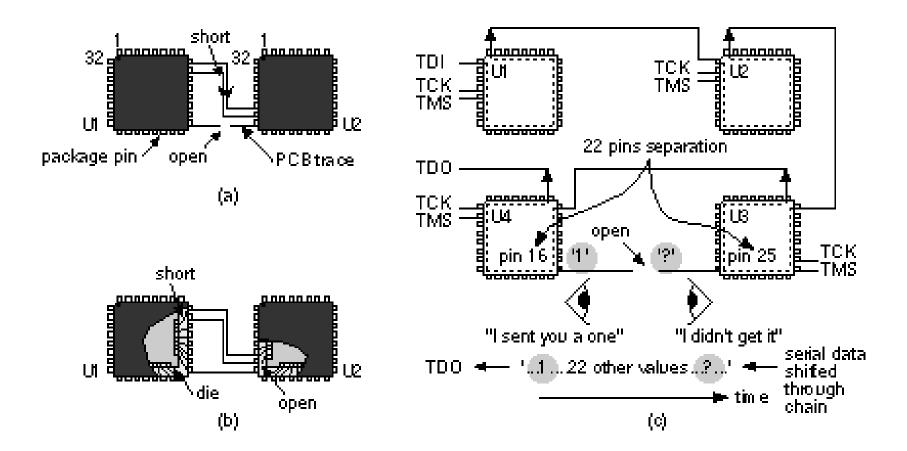

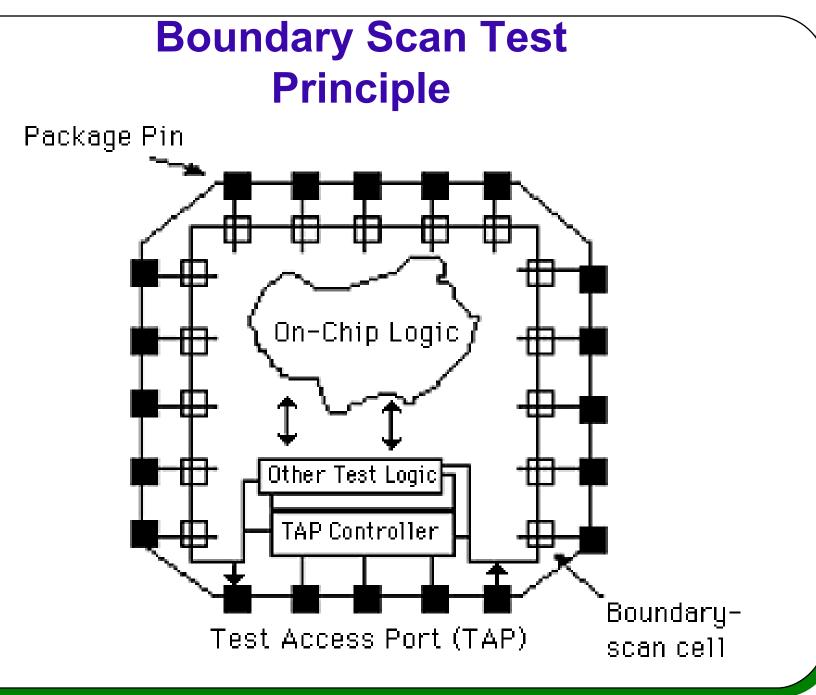

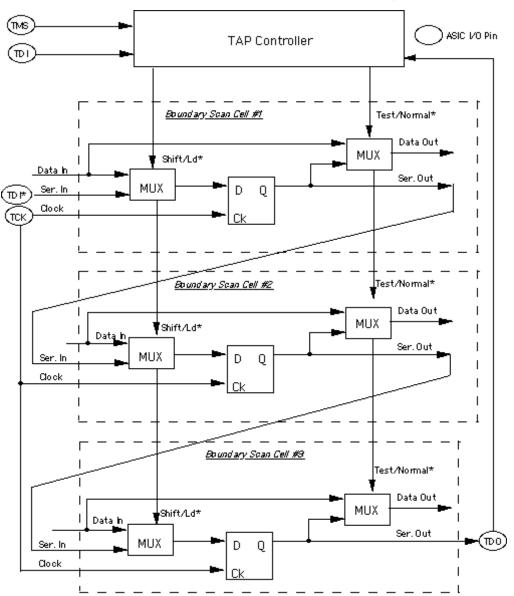

#### Boundary Scan Test IEEE Standard 1149.1

#### Boundary Scan Test Signals

Acronym Meaning BR Bypass register BSC Boundary-scan cell BSR Boundary-scan register BST Boundary-scan test IDCODE Device-identification register IR Instruction register JTAG Joint Test Action Group TAP Test-access port TCK Test clock TDI Test-data input TDO Test-data output TDR Test-data register TMS Test-mode select TRST\* or Test-reset input signal nTRST

#### Explanation

A TDR, directly connects TDI and TDO, bypassing BSR Each I/O pad has a BSC to monitor signals A TDR, a shift register formed from a chain of BSCs Not to be confused with BIST (built-in self-test) Optional TDR, contains manufacturer and part number Holds a BST instruction, provides control signals The organization that developed boundary scan Four- (or five-)wire test interface to an ASIC A TAP wire, the clock that controls BST operation A TAP wire, the input to the IR and TDRs A TAP wire, the output from the IR and TDRs Group of BST registers: IDCODE, BR, BSR A TAP wire, together with TCK controls the BST state

Optional TAP wire, resets the TAP controller (active-low)

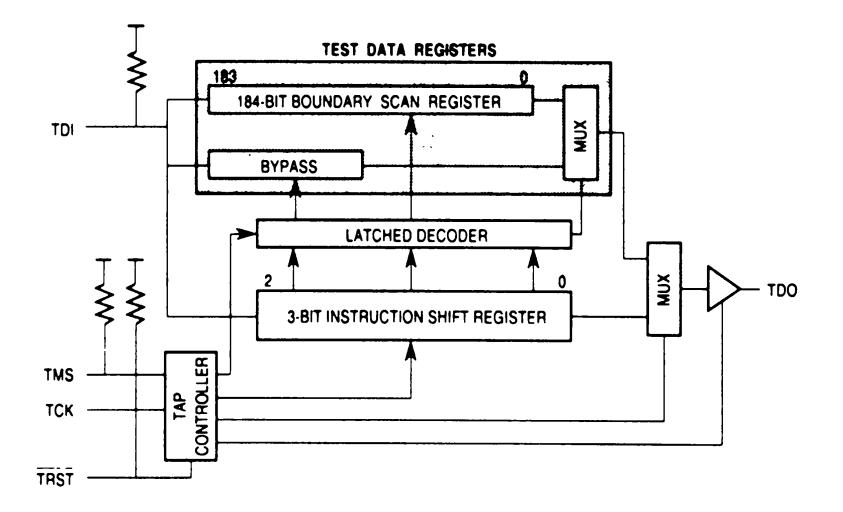

#### **Boundary Scan Test Example (MC 68040)**

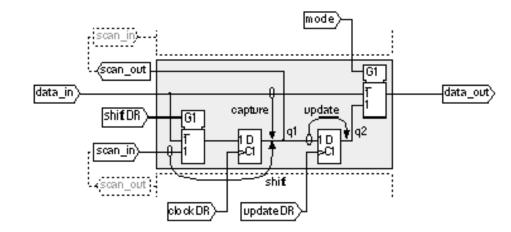

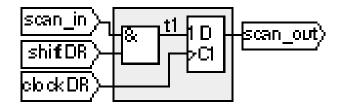

#### Boundary Scan Test DR and BR Cells

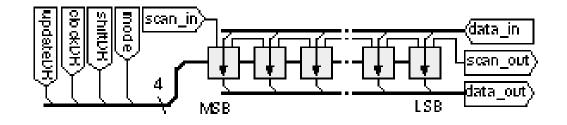

#### **Boundary Scan Register**

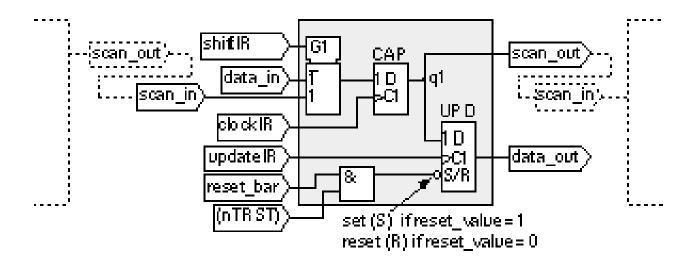

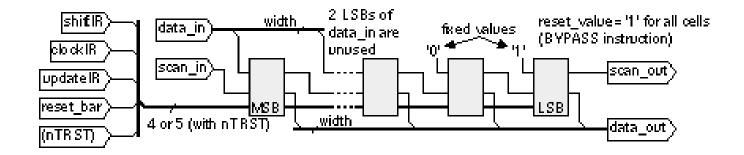

#### Boundary Scan Test IR Cell

#### Boundary Scan Test BSR and IR

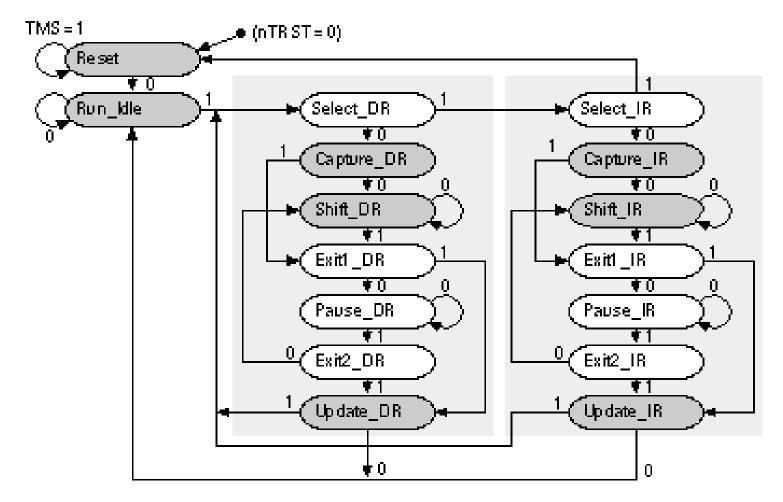

#### Boundary Scan Test TAP Controller State Diagram

### MC 68040 BST Instructions

| Bit 2 | Bit 1 | Bit 0 | Instruction Selected | Test Data Register |

|-------|-------|-------|----------------------|--------------------|

| 0     | 0     | 0     | EXTEST               | BOORSER Scan       |

| 0     | 0     | 1     | HI-Z                 | Bypass             |

| 0     | 1     | 0     | SAMPLE/PRELOAD       | Boundary Scan      |

| 0     | 1     | 1     | DRVCTL.T             | Boundary Scan      |

| 1     | 0     | 0     | SHUTDOWN             | Bypass             |

| 1     | 0     | 1     | PRIVATE              | Bypass             |

| 1     | 1     | 0     | DRVCTL.S             | Boundary Scan      |

| 1     | 1     | 1     | BYPASS               | Bypass             |

#### **Benefits and Penalties of Boundary-Scan**

- Benefits:

- lower test generation costs

- reduced test time

- reduced time to market

- simpler and less costly testers

- compatibility with tester interfaces

- high-density packaging devices accommodation

- Penalties

- extra silicon due to boundary scan circuitry

- added pins

- additional design effort

- degradation in performance due to gate delays through the additional circuitry

- increased power consumption

# Gate requirements for a Gate Array Boundary-scan Design 10000 gate design in a 40-pin package

| Logic Element                                                                                                                                                                | Gate Equivalent                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| <u>Variable Size</u><br>Boundary-scan Register (40 cells)<br><u>Fixed Sizes</u><br>TAP Controller<br>Instruction Register (2 bits)<br>Bypass Register<br>Miscellaneous Logic | 680 аррюх.<br>131<br>28<br>9<br>20 аррюх. |

| TOTAL                                                                                                                                                                        | 868 approx.                               |