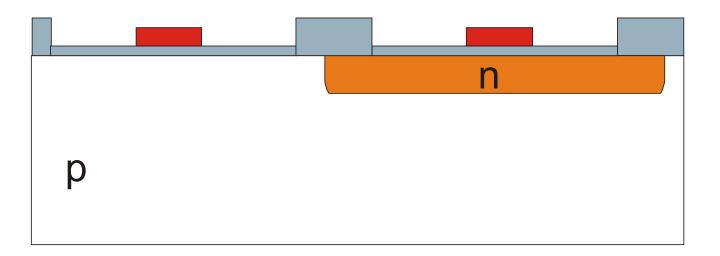

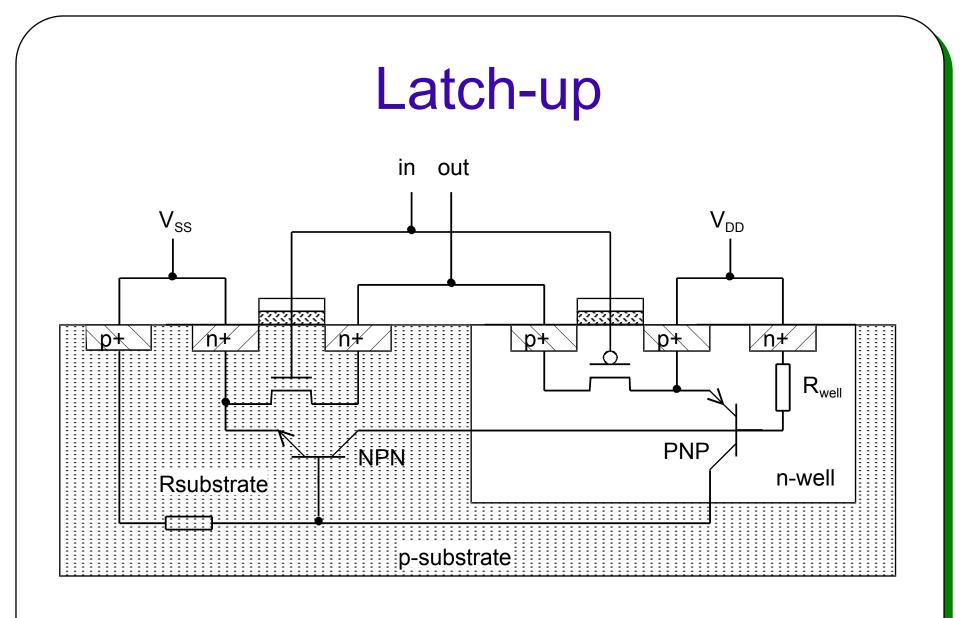

## **N-well CMOS Process**

## **Deposition of Photoresist**

p

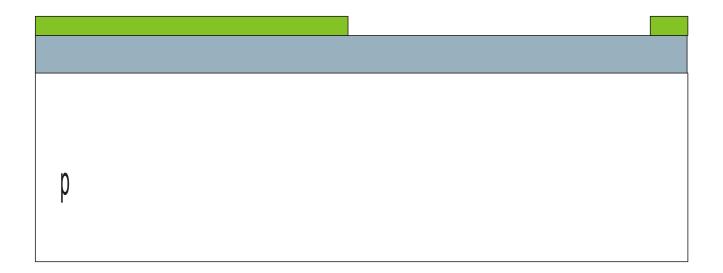

## **Developing of Photoresist**

## Annealling / Rediffusion

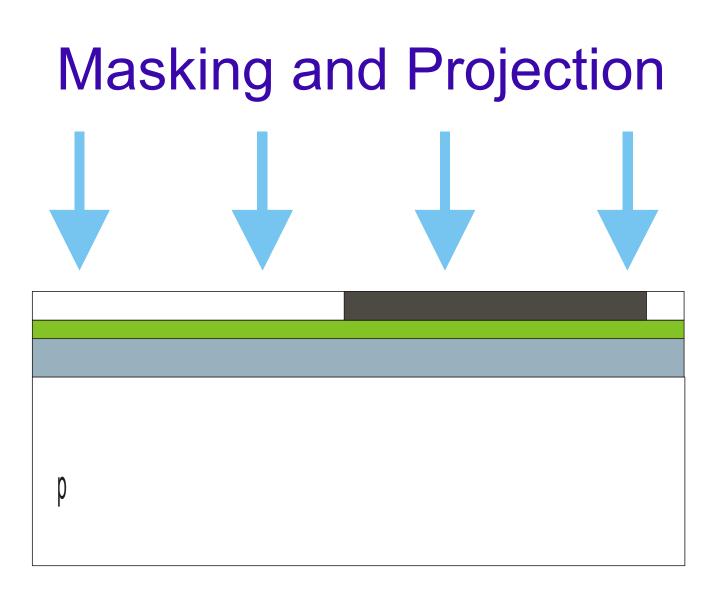

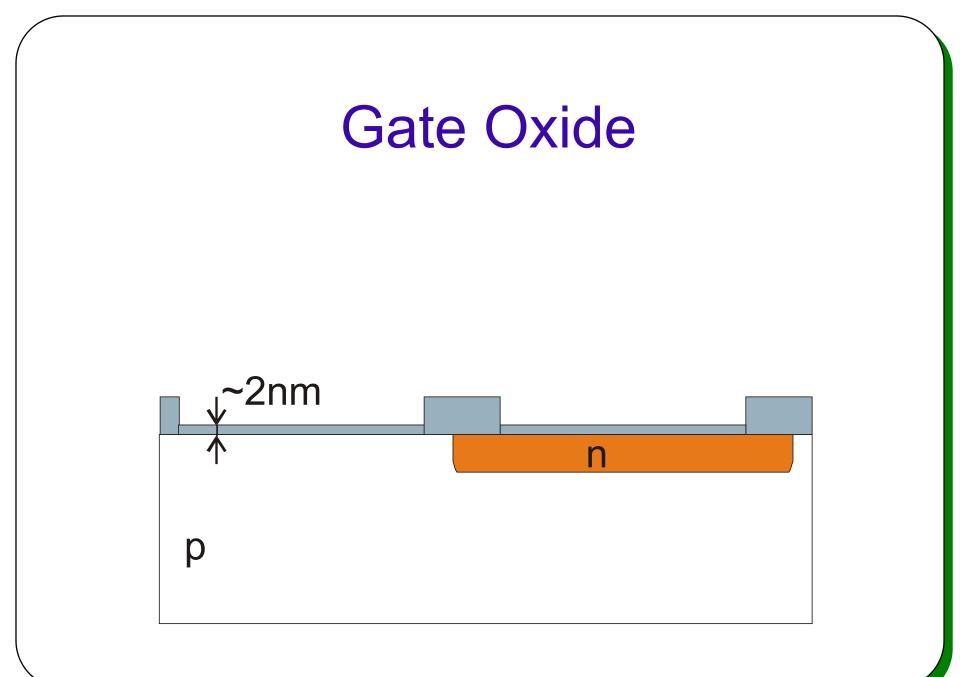

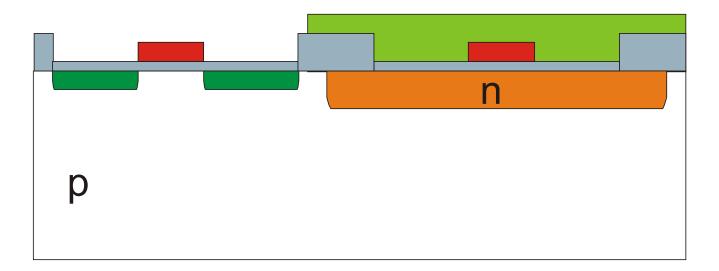

# Deposition, Masking and Etching of Polysilicon

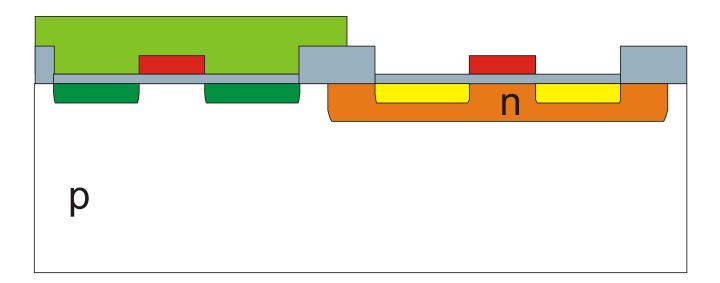

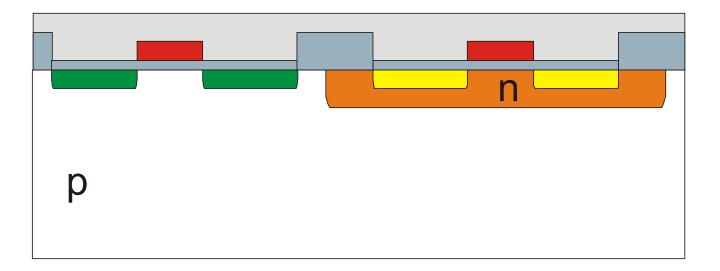

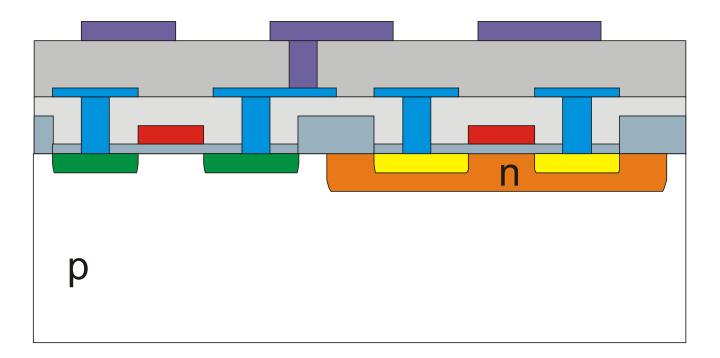

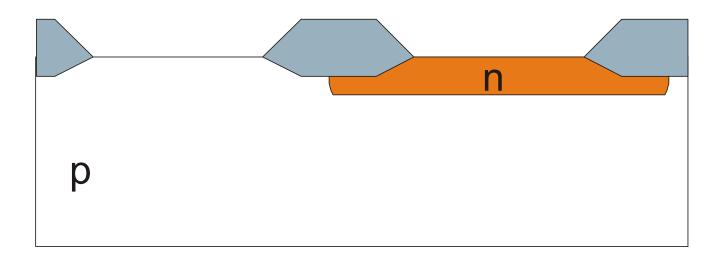

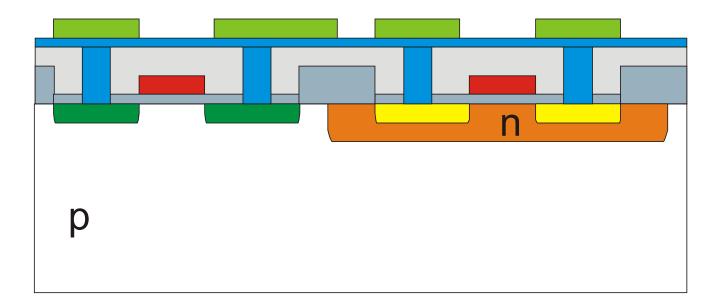

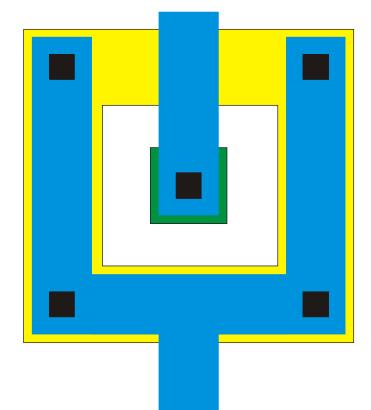

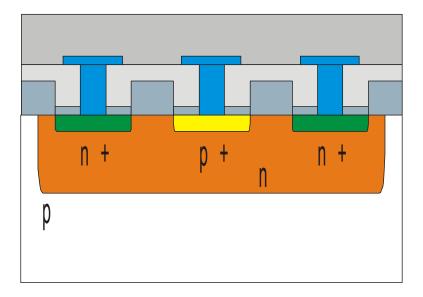

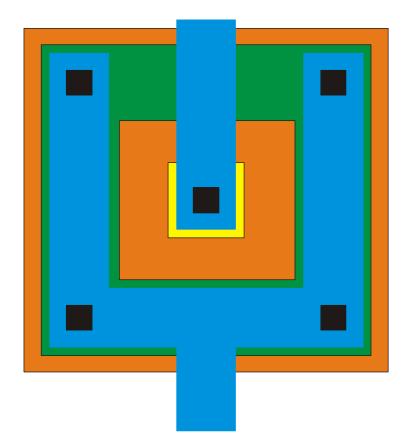

## **NMOS Manufacturing**

## **PMOS Manufacturing**

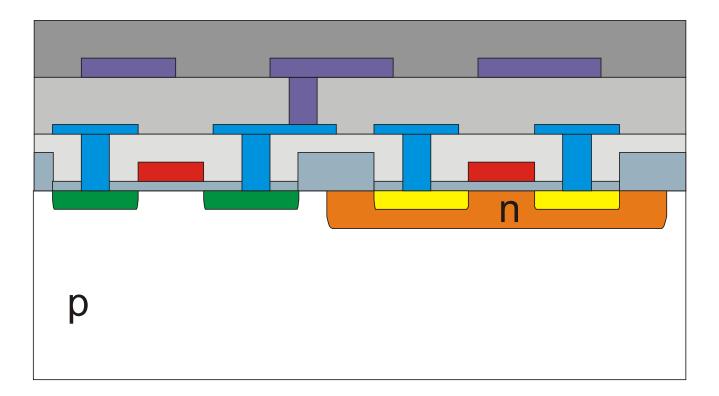

## **First Insulating Layer**

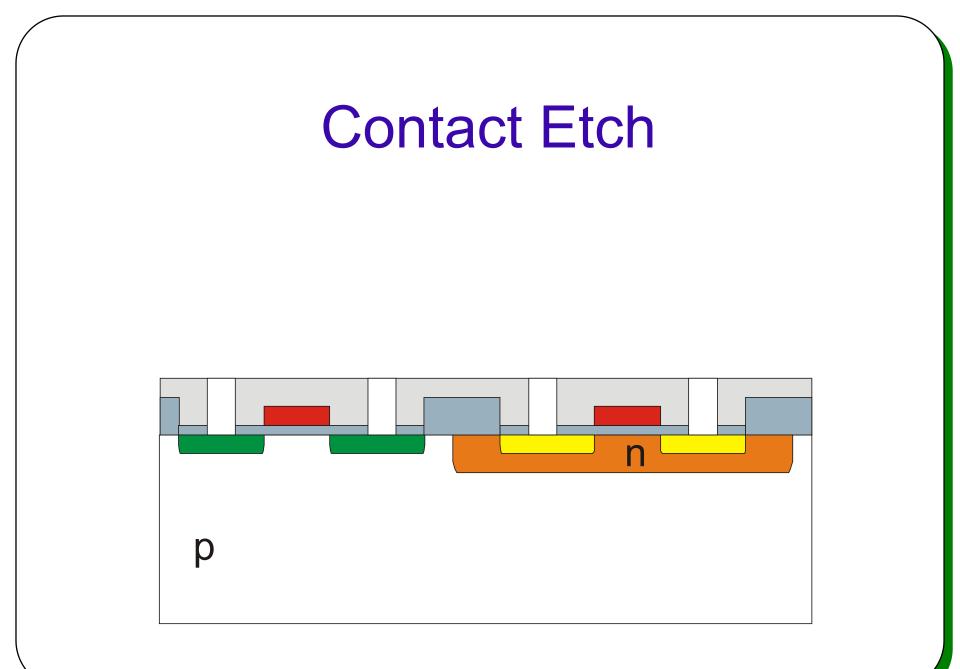

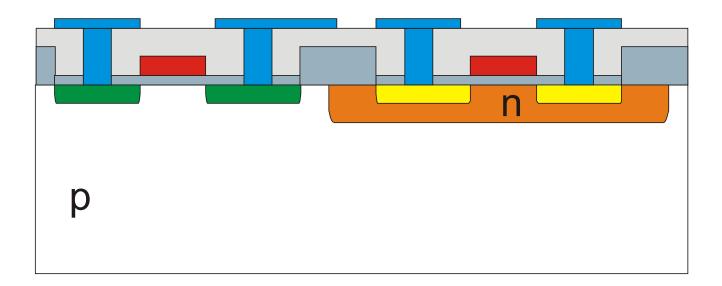

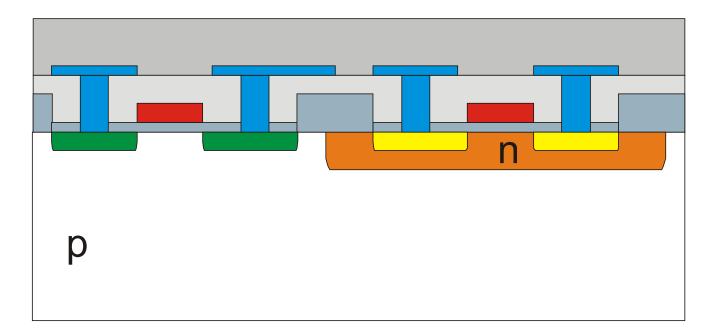

#### **Contacts and Metallization I**

## **Second Insulating Layer**

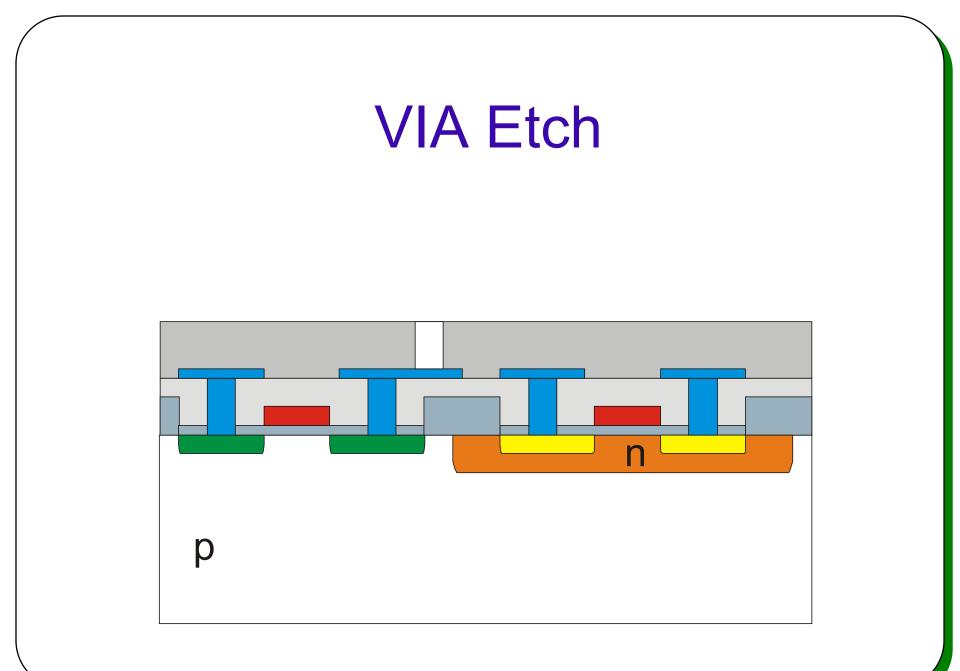

## Vias and Metallization II

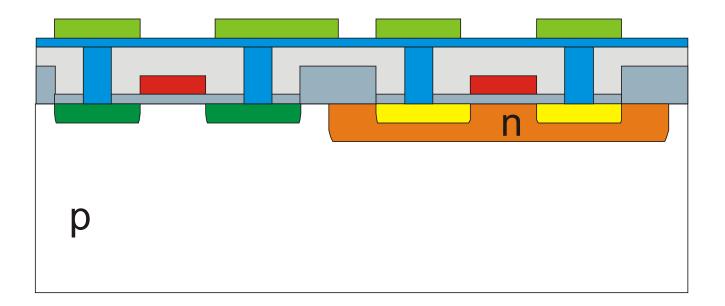

#### **Final Passivation**

#### **Deposition of Metallic Layers**

# Etching Away of Excessive Metal

#### **Metal-Semiconductor Contacts**

- Drain and source pins

- Substrate and well bias

- Always to heavily doped semiconductor

- Iow ohmic resistance

- no Schottky junction

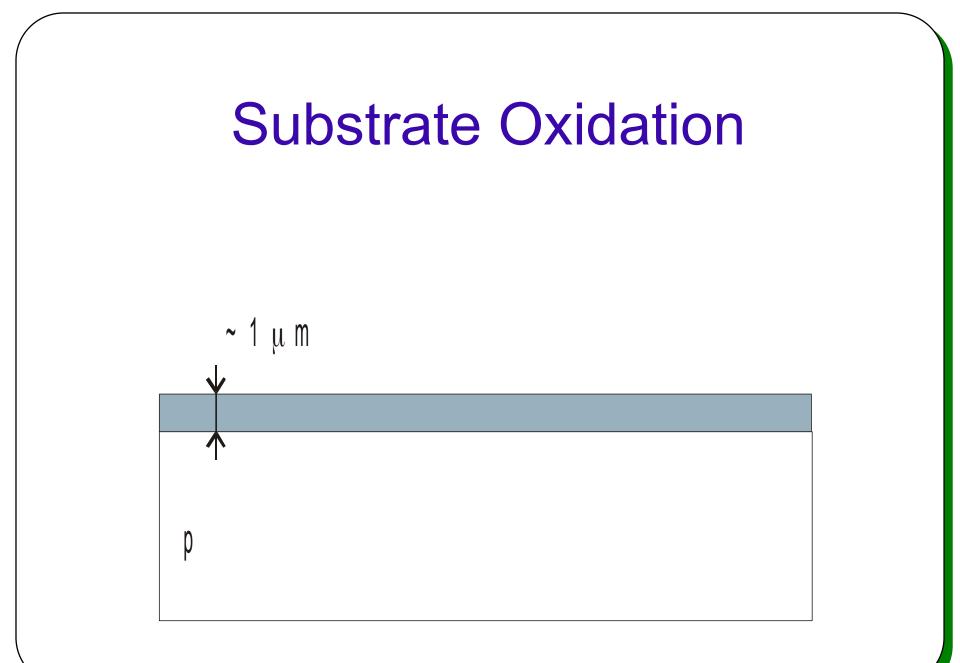

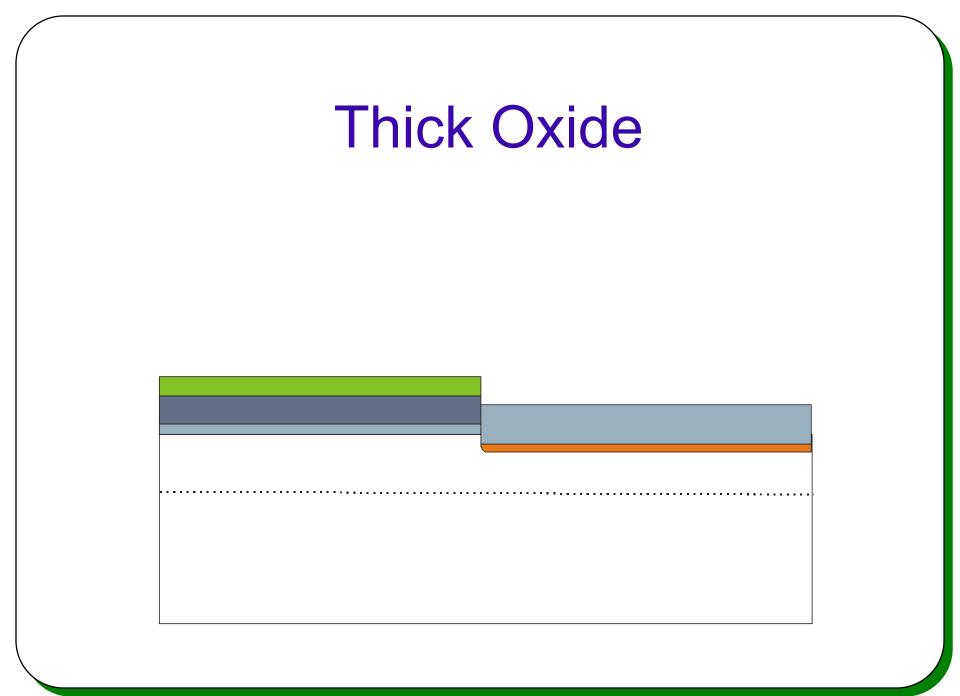

## LOCOS Technology

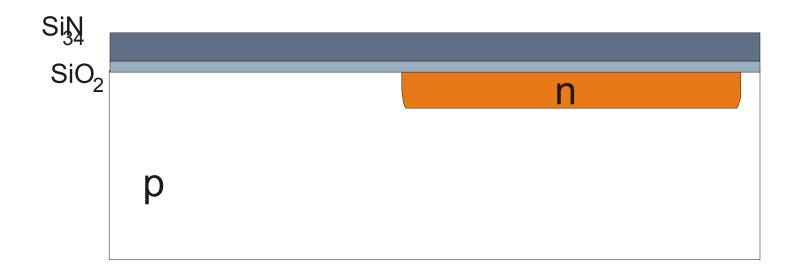

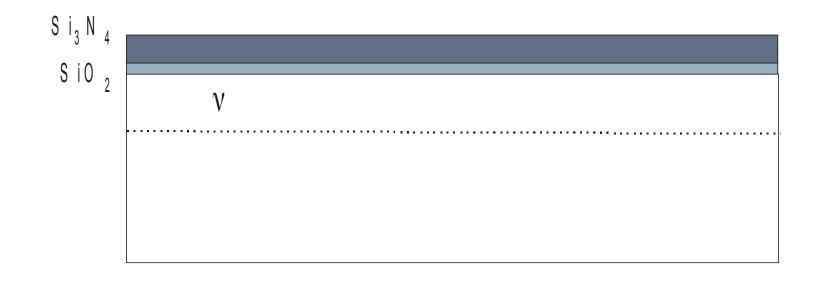

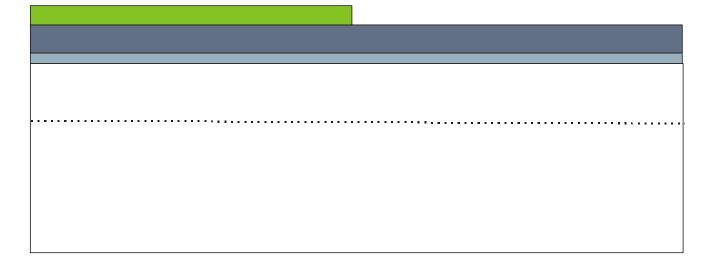

## Deposition of Silicon Dioxide and Silicon Nitride

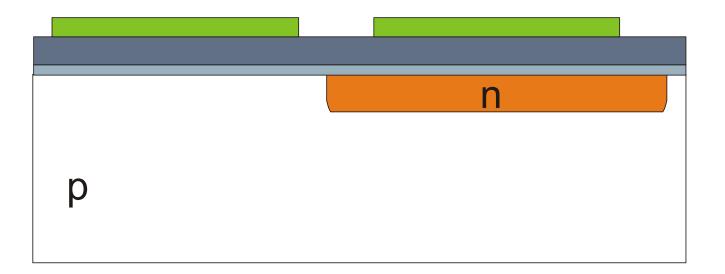

## Deposition, Masking and Etching of Photoresist

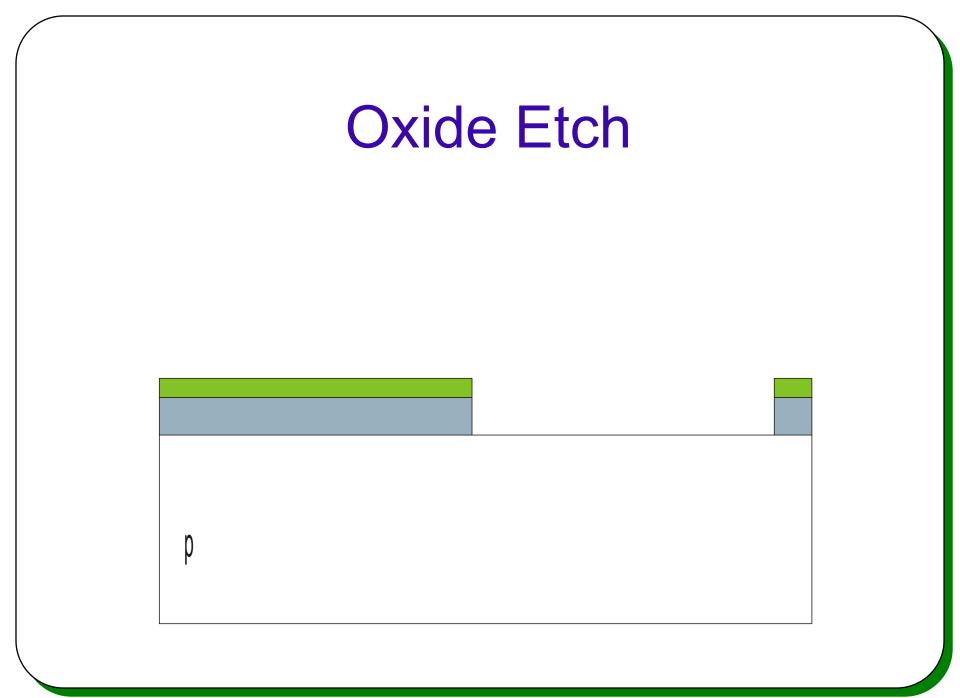

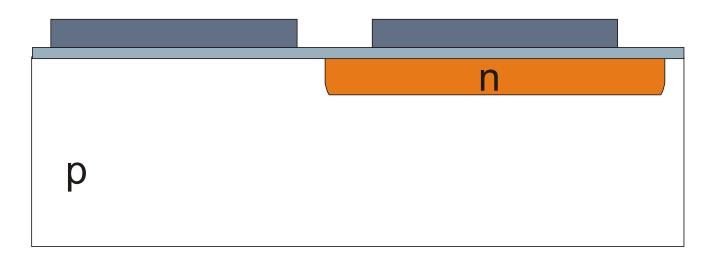

## Etching of Nitride and Removal of Photoresist

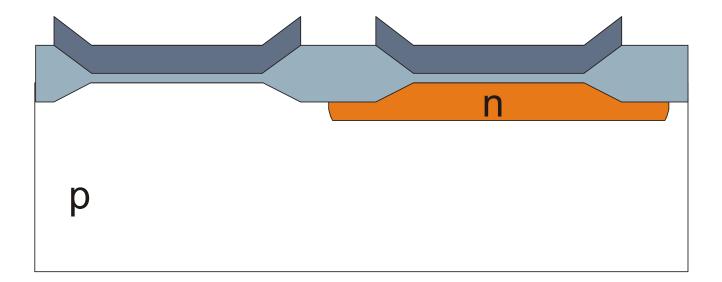

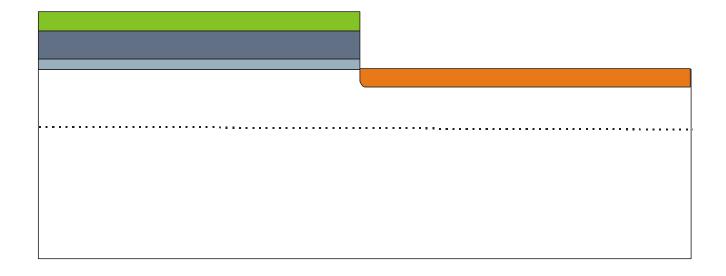

## Field Oxide Manufacturing

# Removal of Nitride and Thin Oxide

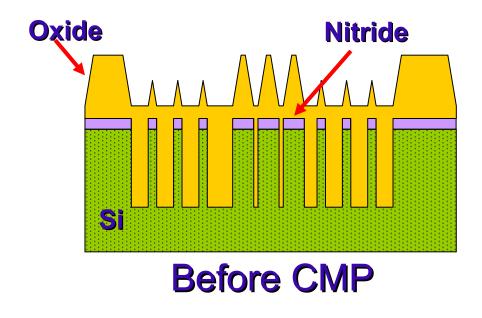

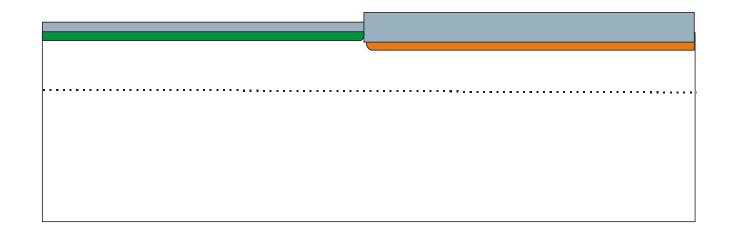

## Shallow Trench Isolation (STI)

## **LOCOS Shortcomings**

- In submicron technologies (below 250 nm) LOCOS isolation takes too much space

- The mechanical stress appearing at thin/thick oxide border increase the gate leakage current

## **Shallow Trench Isolation**

- Curently the most commonf form of isolation

- Trenches in substrate filled with oxide surrond the devices and isolate them from the surroundings

#### Process steps:

- Diffusion areas covered with nitride

- Trenches etched and filled with CVD oxide

- CMP (Chemical and Mechanical Polishing) removes the unneeded oxide

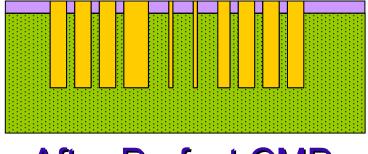

#### **Shallow Trench Isolation**

After Perfect CMP

# Twin-Well (Twin-Tub) Technology

# Epitaxial Layer Covered by Oxide and Nitride

Photoresist Deposition, Projection, Developing and Removal

### **N-Well Implantation**

### **P-Well Implantation**

## Annealing / Rediffusion

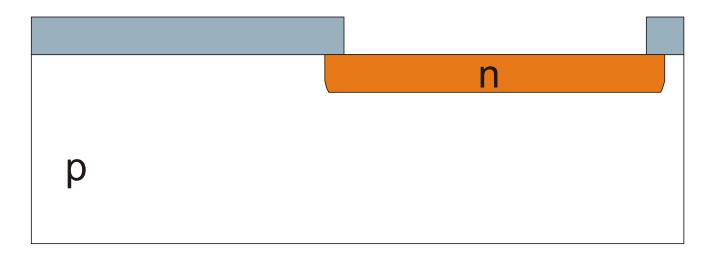

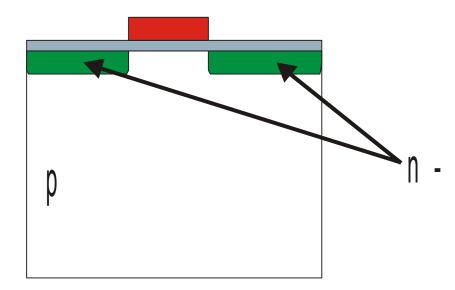

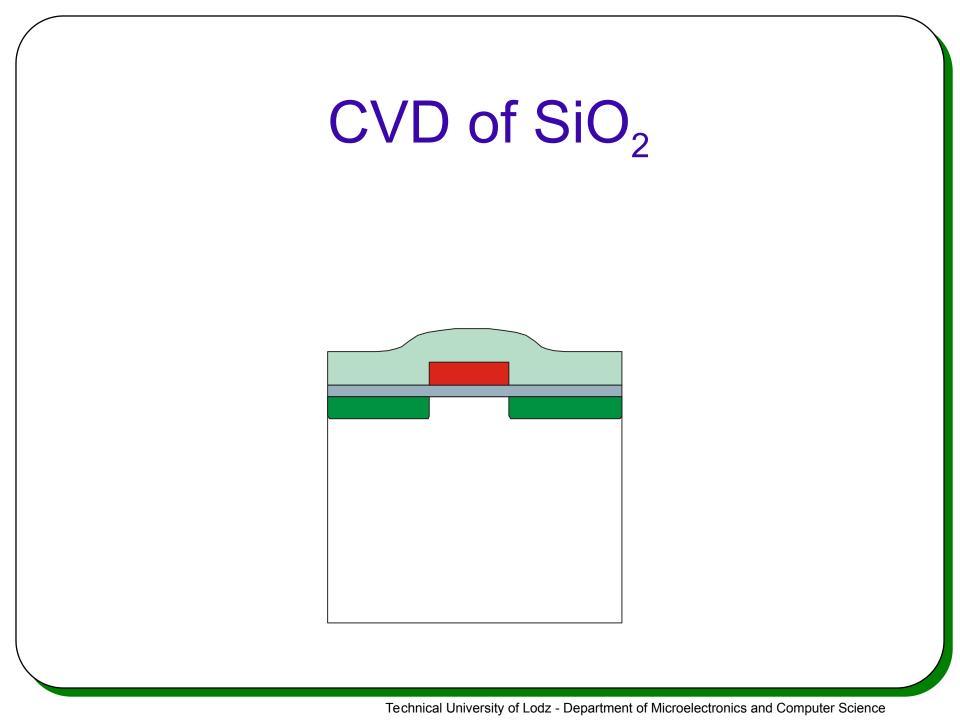

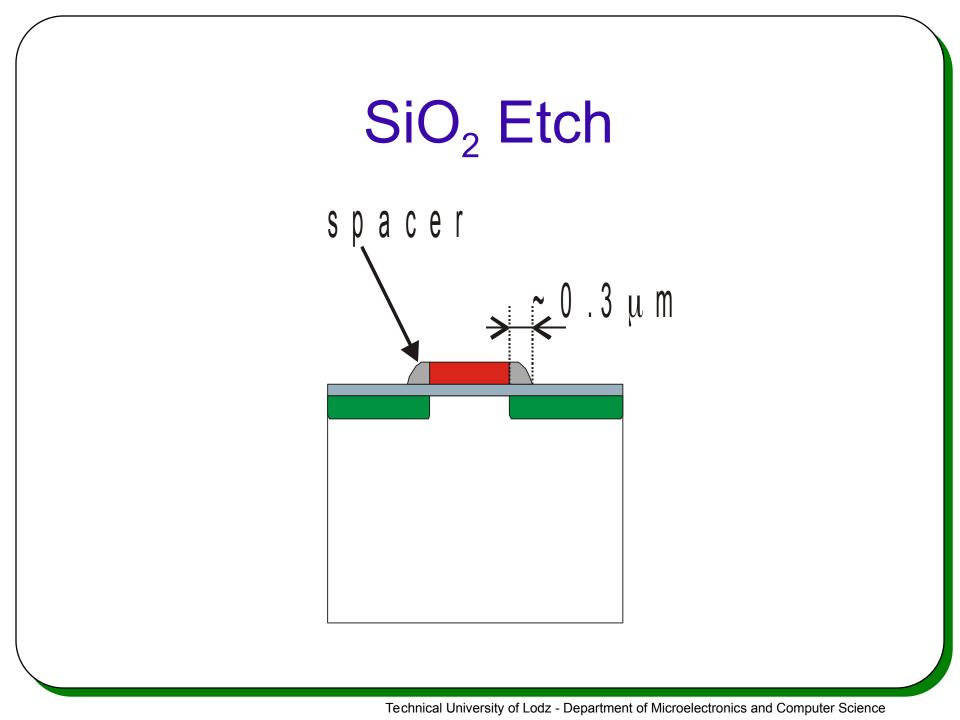

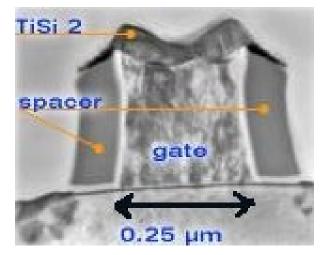

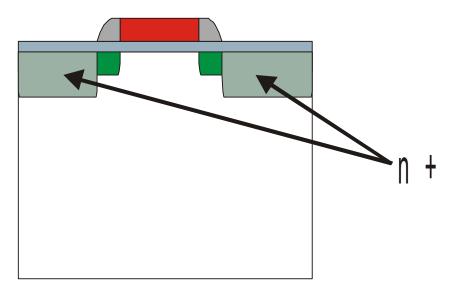

## Lightly Doped Drain (LDD) Transistor

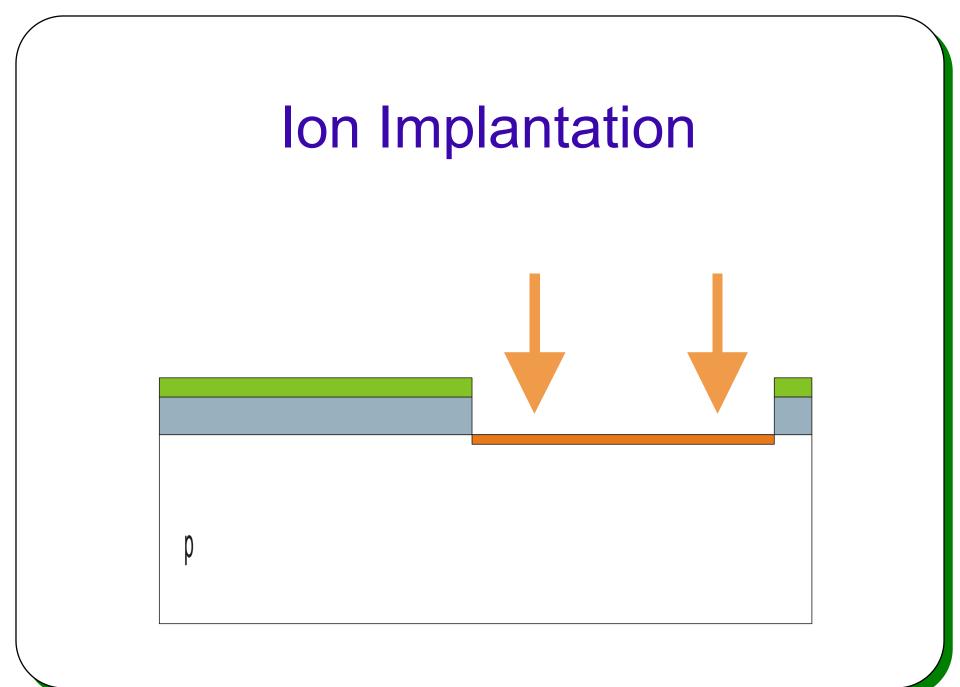

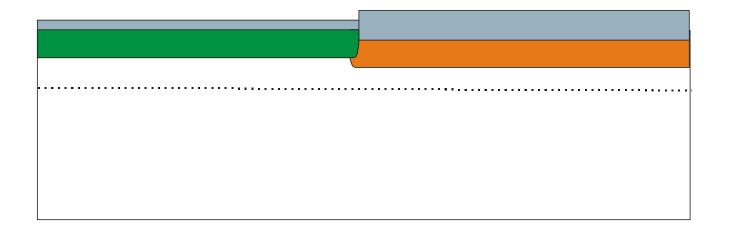

## Implantation of Lightly Doped Drain and Source Areas

## **Drain and Source Implantation**

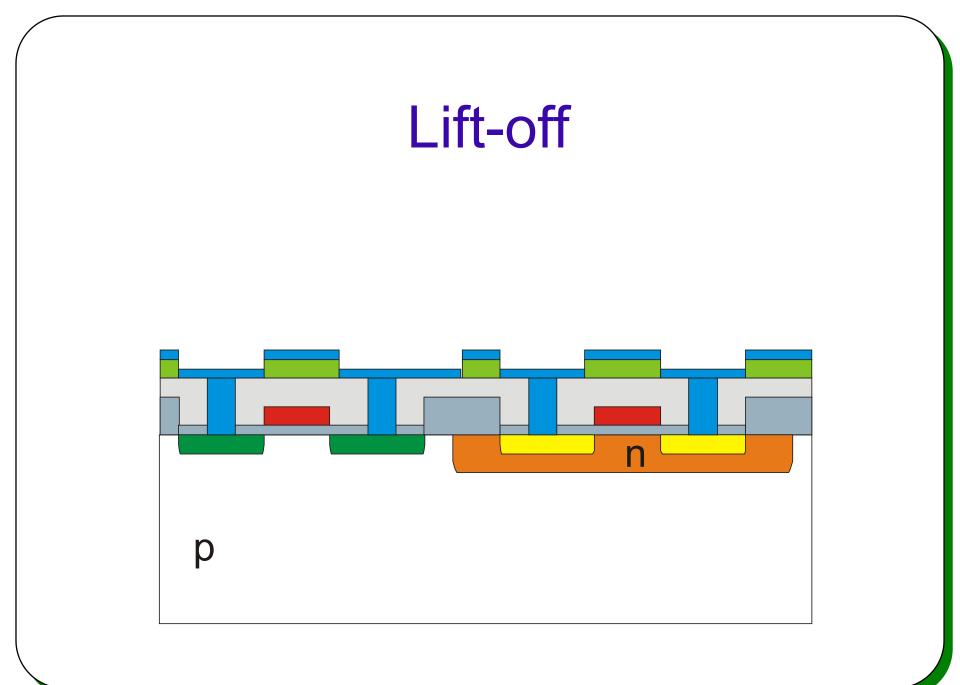

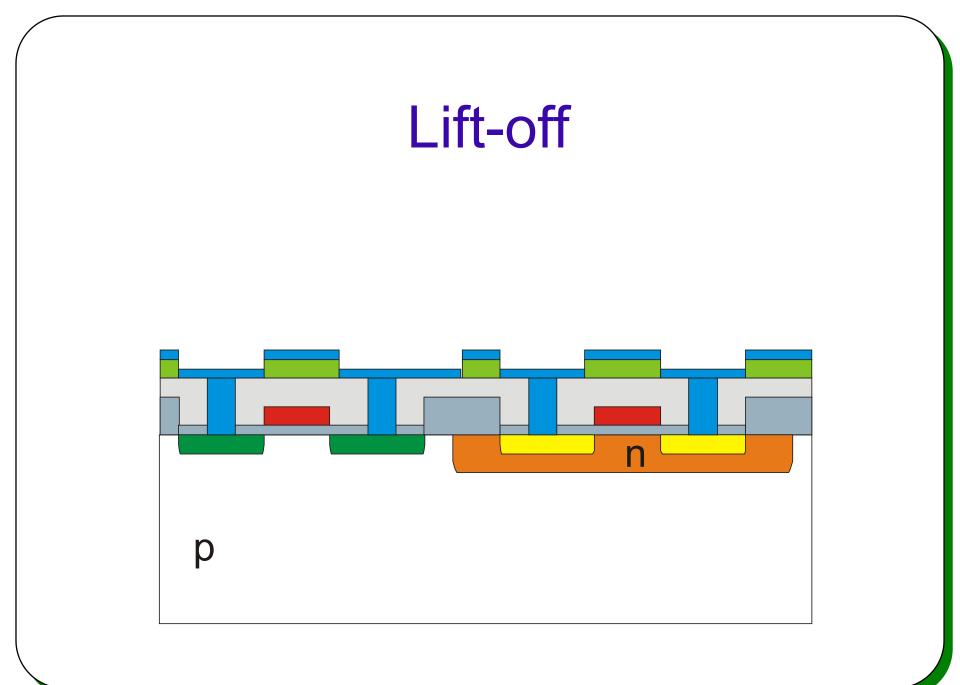

### Interconnection Manufacturing

## **Etching of Surplus Metal**

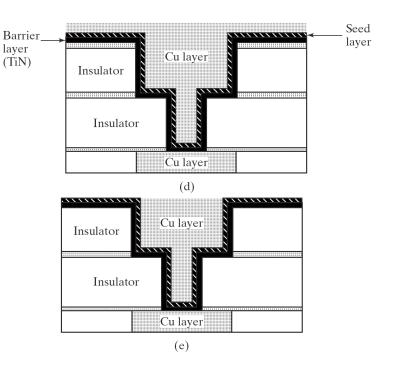

## **Copper in Interconnection**

- Conductivity of Cu 50% greater, than Al

- Gives better results as the material for interconnections

- Disadvantages

- Hard to dry-etch, different methods of manufacturing needed

- Quickly diffuses in silicon

## Interconnection Delay Components

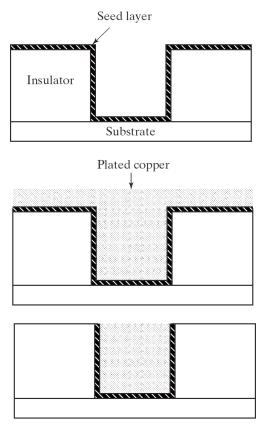

## The Damascene Process

### Process steps:

- Deposition of insulation

- Etching of trenches

- Seed layer deposition (PVD)

- Electroplating with copper

- CMP

(b) Copper Damascene process

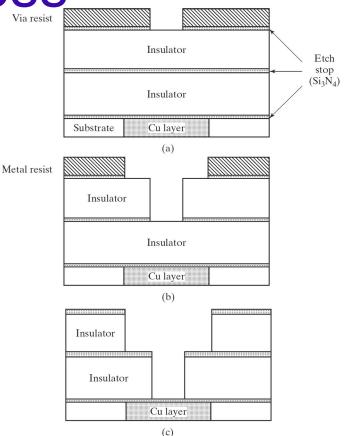

## The Double Damascene Process

- Process steps:

- Deposition of two insulation layers separated by nitride (etch stop)

- Via mask and etching including the buried nitride layer

- Metal mask and etching through two insulator layers

# The Double Damascene Process (contd.)

### Then:

- Deposition of barrier layer (TiN)

- Deposition of metal (PVD)

- Electroplating

- CMP

## n+/p Diode

## p+/n Diode

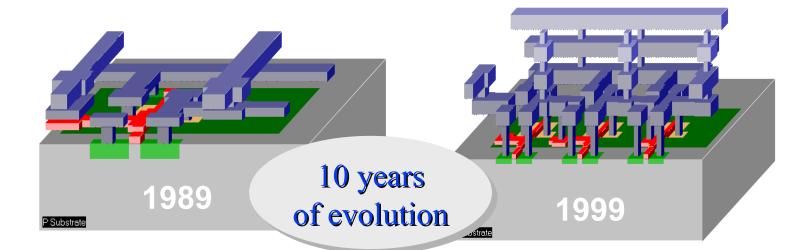

### **Technological Advances**

### 0.7µm technology

- <sup>©</sup> 0.7μm, 2 metal levels

- <sup>©</sup> over 100,000 transistors/die

- © clock frequency: 50MHz

### 0.18µm technology

- $^{\odot}$  0.18µm, 6 metal levels

- over 10,000,000 transistors/die

- © clock frequency: 500MHz

### 40 pins

**512 pins**

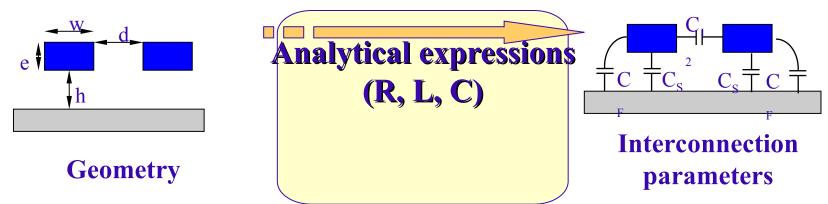

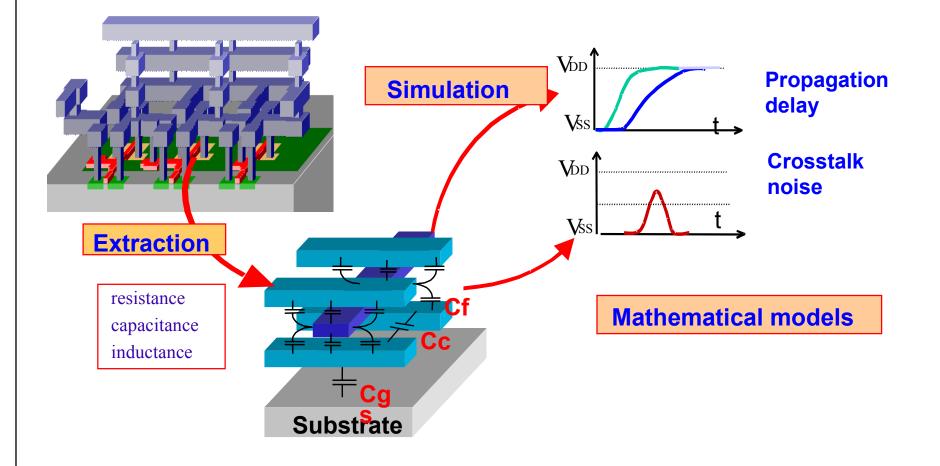

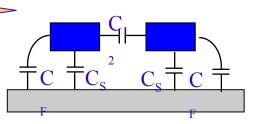

### Interconnection modelling

### Interconnection modelling

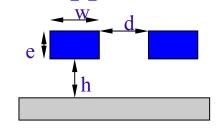

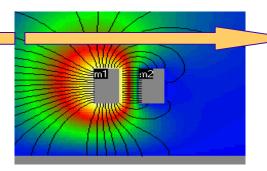

### •Field approach

Geometry

#### Interconnection parameters

### Analytical approach